Other Parts Discussed in Thread: DS90CR481

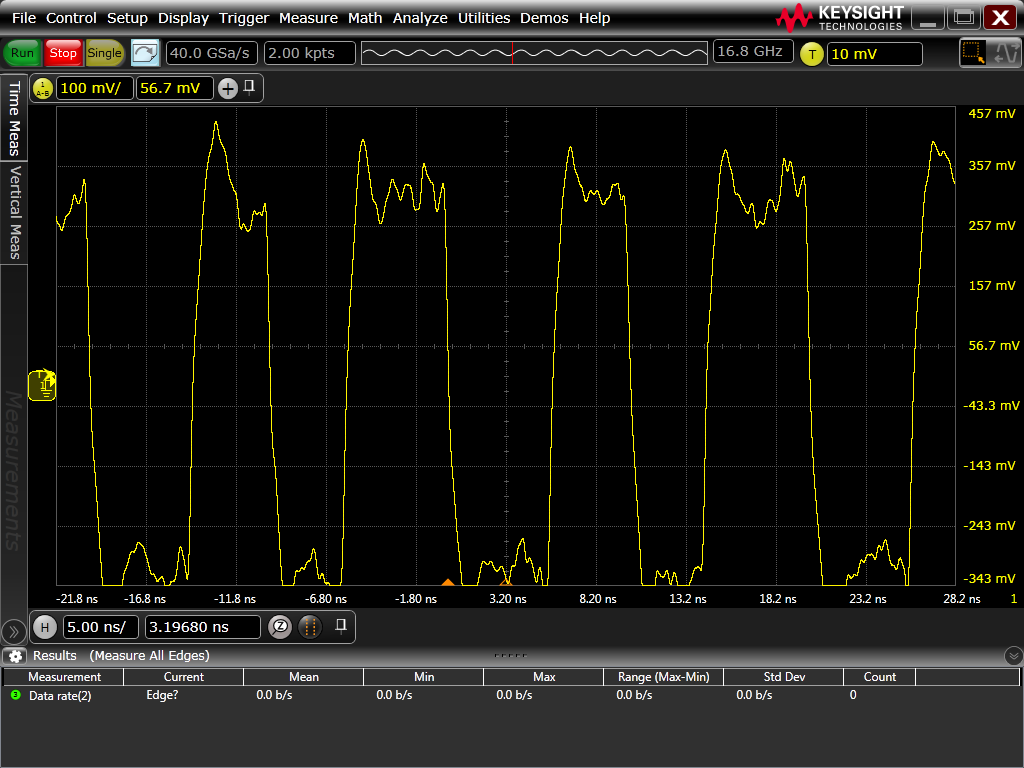

Hi, I'm using the DS90CR481, data sheets say, LVDS clock signal shall be

"1111000" or "1110000" pattern, but it's seems "11110000" and "111000" on DS_OPT applied high and BAL applied high

of clock_in @100MHz. is it something wrong using?