Hi,

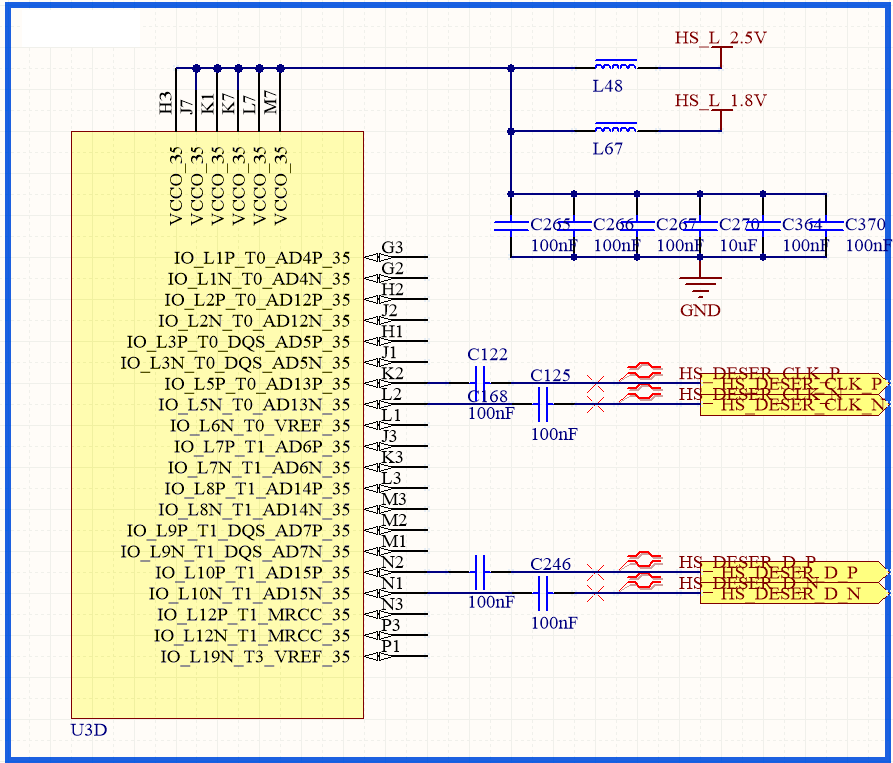

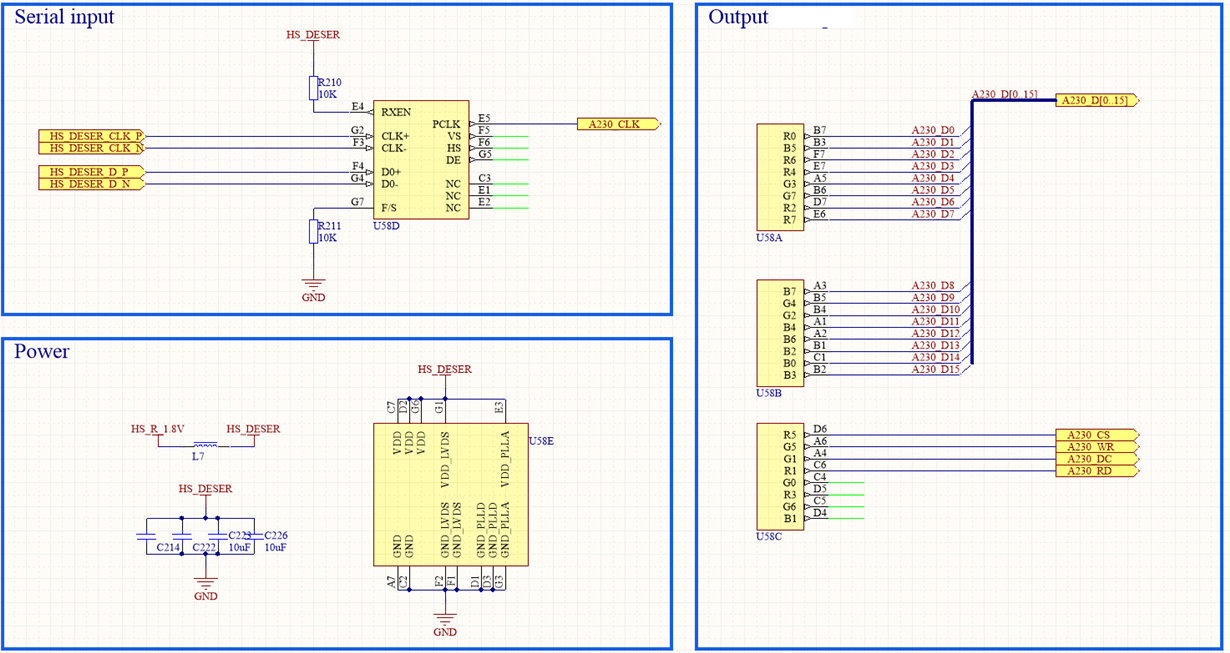

We're working on a project with very tight space constraints, and are in need of a SER/DESER solution to carry data from our Artic7 FPGA. Given the space constraints, we are looking to use the Artic7 as a SER and connect 2 of its LVDS outputs directly to a SN65LVDS310.

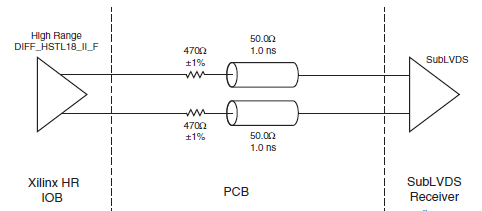

There is a potential problem of LVDS<>SubLVDS mismatch, but based on Xilinx' xapp582 we decided to invest time in a small testboard (since devkits are not available and our local rep couldn't get us anything similar). xapp582 advises to put series resistors close to the transmitter, which we did to get the signals within the recommended operating range of the SN65LVDS310.

Below is a screenshot of how what the 4.167MHz clock signal towards the SN65LVDS310 looks like. Yellow/blue are the CLK+/-, red is their difference, indicating a 176mV differential amplitude, well within the 70mV-200mV range specced in the SN65LVDS310 datasheet. (measure using 1GHz passive probes on 1GHz bandwidth scope, 1MOhm termination)

However, the SN65LVDS310 is not reacting at all. Regardless of the Data lines (which are presenting a fixed value at the same voltage levels as the clock), we believe the SN65LVDS310 is supposed to produce a 4.167MHz clock. But the clock output is staying low, as well as DE; while other outputs are high. (most signals connector to other non-driving ICs; while the clock output is floating)

Can you please recommend how we should attempt to get the output clock running?

Additional information:

- Stable 1.78V on all supply pins (All VDD types shorted together)

- RXEN pulled up to VDD using 10Kohm (1.78V on RXEN side)

- F/S pulled down using 10Kohm

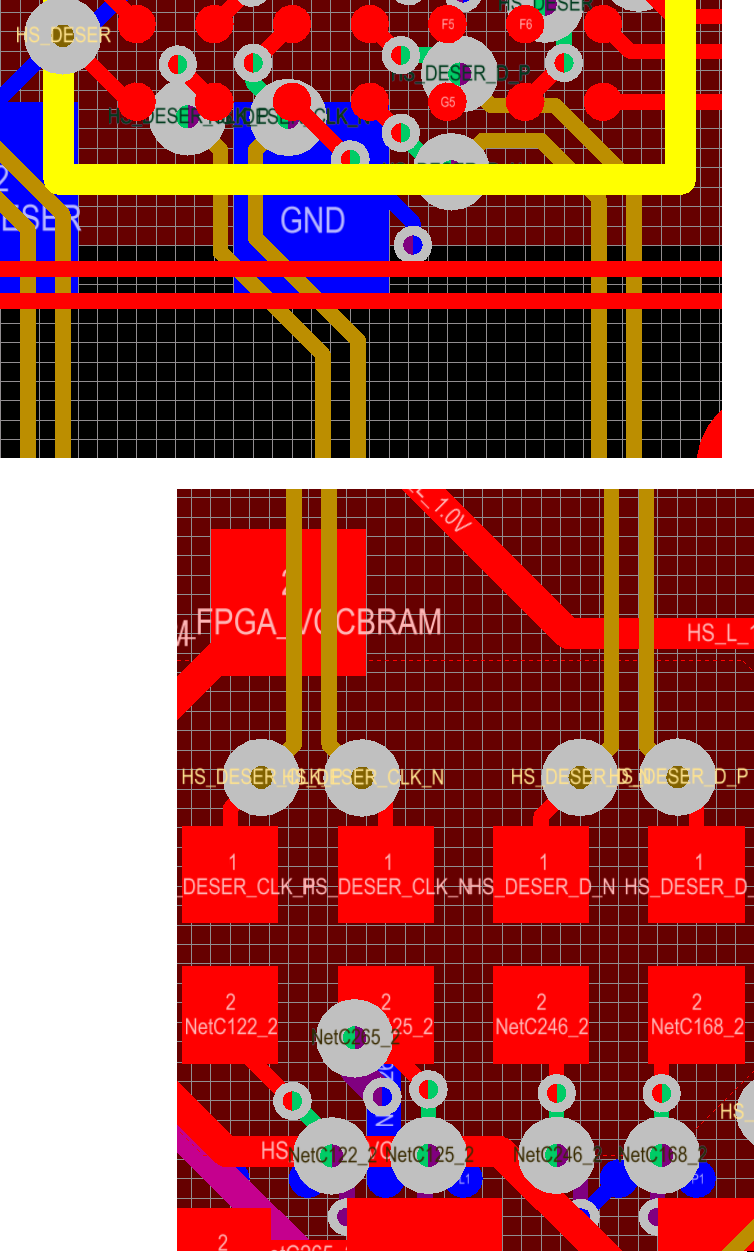

- Traces between transmitter resistors and receiver routed as 100ohm diffpair, 3cm runlength (see below)

- No termination resistors used at receiving side (as they are assumed to be internal) (see below)