I have two TUSB1310A on my board (USB 3.0 protocol analyzer design). Both reset fine and de-assert PHY_STATUS. Both output 250 MHz PCLK and both detect LFPS fine. Scope shows good eye diagram at both SSRX pins. However, only one of the PHYs actually lock onto data (PHY A). The other one (PHY B) only de-asserts RX_ELECIDLE and never passes any RX data.

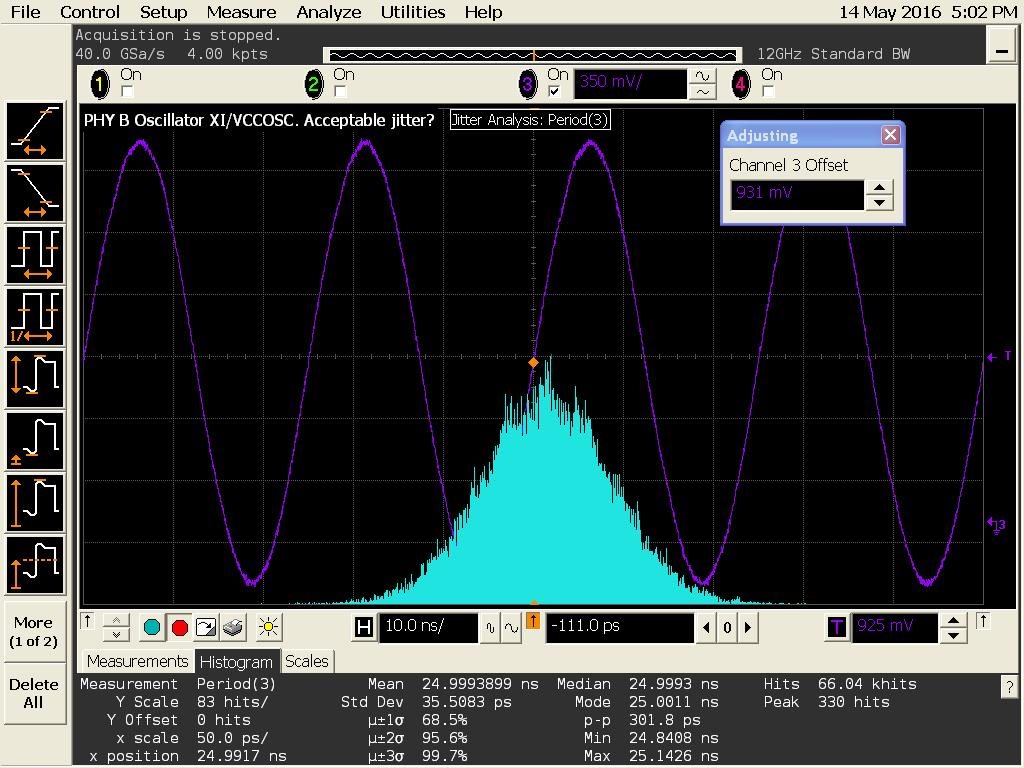

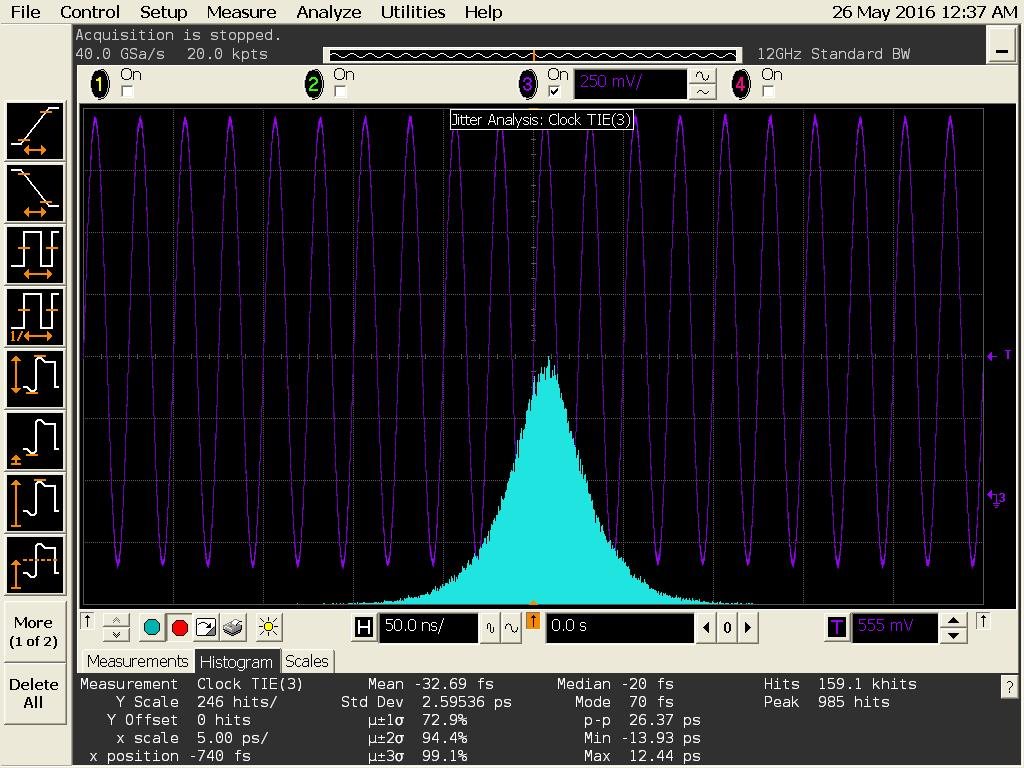

I have measured the oscillator cycle-cycle jitter (external 40 MHz XTAL) and get the below results. This is measured across the XI/VSSOSC capacitors:

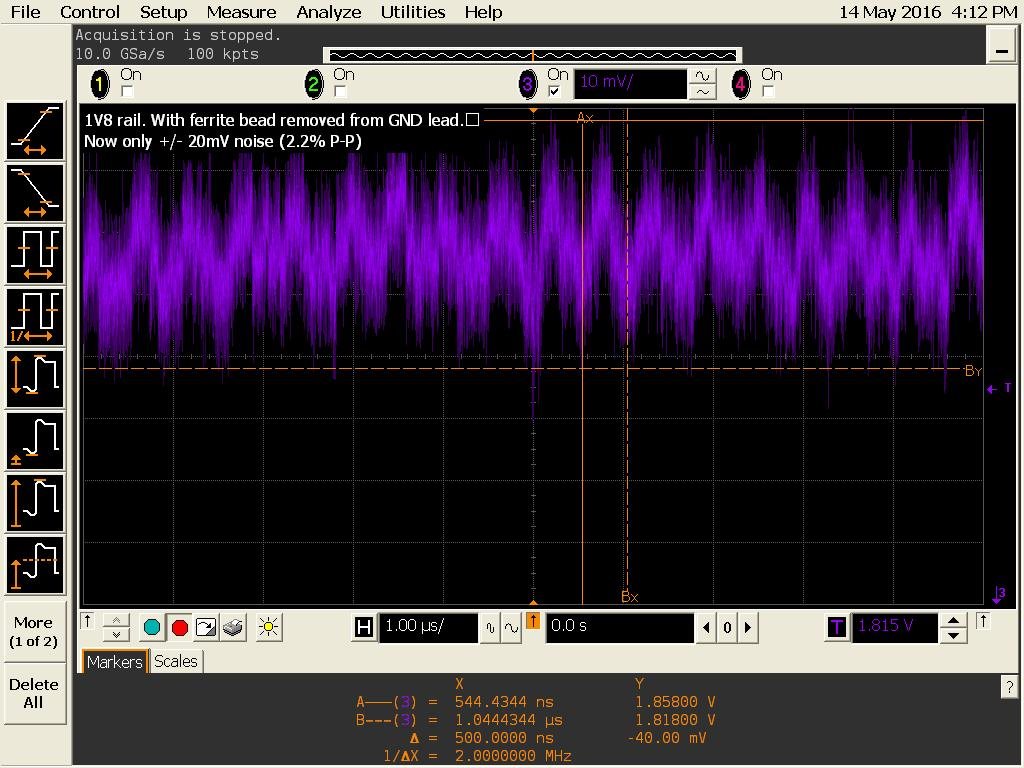

My scope shows the p-p jitter around 300ps. Is this too high? The datasheet says that an external oscillator should have "absolute p-p" 50ps or less but what about the built-in oscillator? The 1.8V power rail to the TUSB1310A is quiet, with about 40mV p-p per below scope screen shot.

If the jitter is too high, what specs should I use? 1 sigma, std deviation or max p-p? What jitter should PCLK have? Too high (due to power supply noise, for instance, could interfere with data lock?).

Thank you.

/John