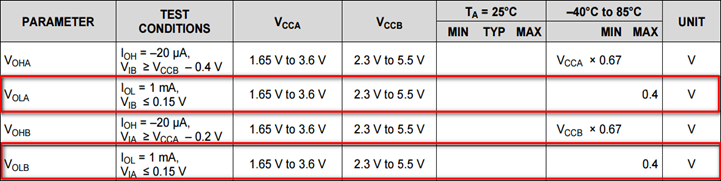

customer report the more devices's VOL might be higher than TCA9406 VIL spec define(0.15V max).Is there any risk in if another devices' VOL higher than VIL of TCA9406? Is that the issue make the TCA9406 function/level conversion fail?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.