Other Parts Discussed in Thread: DS125BR820, DS100BR111, DS125BR111, DS80PCI810, DS110DF111, DS110DF410

Hello,

I have some questions:

1) what is the difference in structure between DS125BR820 and TLK1102E, one is categorized as repeater and the other as equalizer? (can they be used interchangeably?)

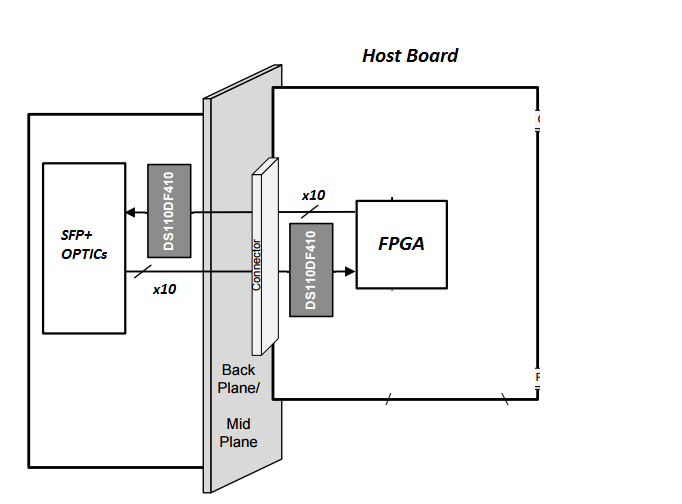

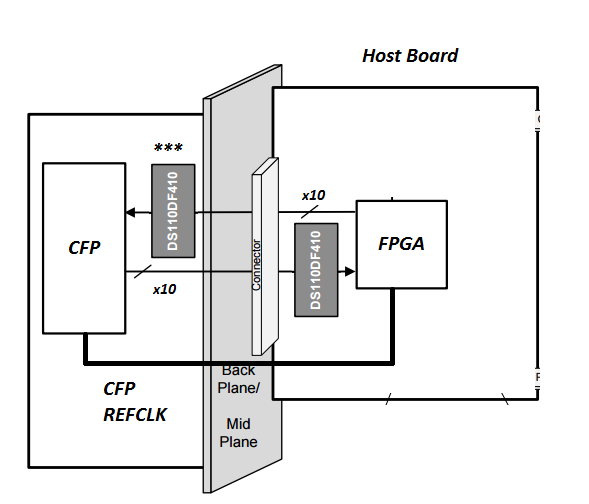

2) In our customer application we have this situation:

main FPGA ---- about 10" FR4 --- Molex Connector ---- about 5" FR4 --- SFP+ Optics

which one of these parts is best fit?