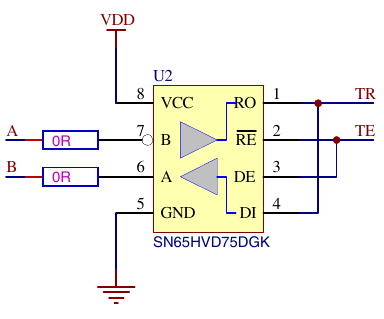

I am using this SN65HVD75DGK chip in a design and find that it generates a 50ns to 300ns low glitch on the R data line about 70ns after TE goes low. The configuration joins /RE with TE and R with D but I have managed to do some surgery on the msop package to tie /RE low but the glitch is still there. I can shorten the glitch by biasing the line but I can't get rid of it. It doesn't change anything much if I have termination or not or totally remove the cable.

BTW, I have floated the D&T lines and pulled them up with 1k and simply pulsed the TE and the same thing happens so it has nothing to do with the MCU etc. If I try to drive the R line for a few hundred nanoseconds after TE goes low I can see the 65HVD75 winning the battle and holding the line low. If I put a 330R resistor in the R line I can override the glitch but it's a kludge. I am operating at 1Mbit at present just for these tests but the glitch is way too long for higher baud rates. Of course I could get around it in software but my logic analyzers don't like it much.

Now this is a serious question and not meant to be critical but do all the TI fail-safe chips that aren't supposed to glitch do this? I can't go trying them all and the msop pack limits what I can use.

Peter