Other Parts Discussed in Thread: SN65DSI84

Hi all!

I have some questions about sn64dsi84 and I would like some help, please.

I've started working on a Jetson-TK1 platform that has two sn64dsi84 bgas to drive two lvds 1920x1080 monitors.

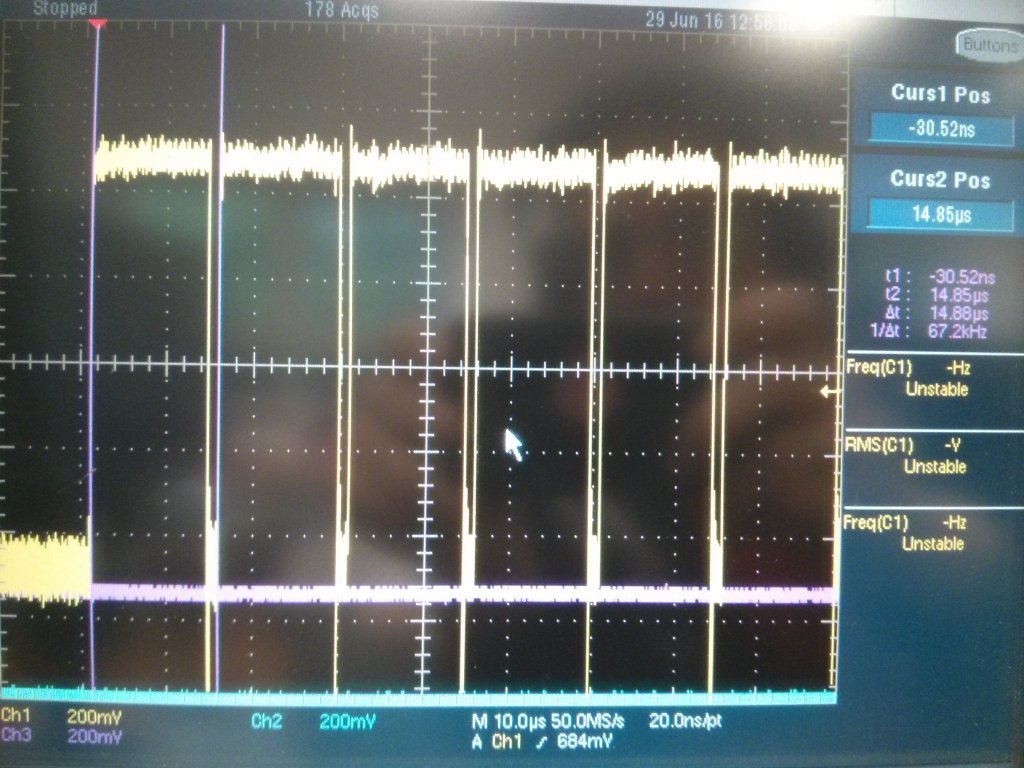

The board is ready, I've made almost everything working and now I have to bring-up the displays. I'm trying to i2c probe the chip from u-boot but it doesn't respond to any i2c commands (100KHz). I've validated the i2c commands with a scope and they are fine. The datasheet mentions that the dsi lines have to be in LP11 state to have access to the i2c registers. This means that the chip won't reply at all to any commands if the dsi output is not in LP11 state?

Only by following this init sequence the chip responds to i2c commands?

Also I'm bit confused about the i2c addresses. The datasheets refers that depending the address pin the addresses are 0x58/0x59 or 0x5a/0x5b for w/r. On the other hand there is an example script (8.2.2.1 in the datasheet) that uses the address 0x2d. The weird thing is that also the dsi2lvds driver on the tegra linux kernel uses that address, too. Also in the kernel driver there's no such init sequence that puts the dsi in low power mode to access the external dsi2lvds converter.

Do you provide a driver or I have to implement it by myself? It would be very convenient for developers if such driver existed, especially now that the tegras are so up-market and many manufacturers still using lvds displays.

Thank you in advance!

PS. I also have some other questions regarding the dsi tool and the parameters but first I have to bring up at least the displays.

Dimitris.