Hello Community,

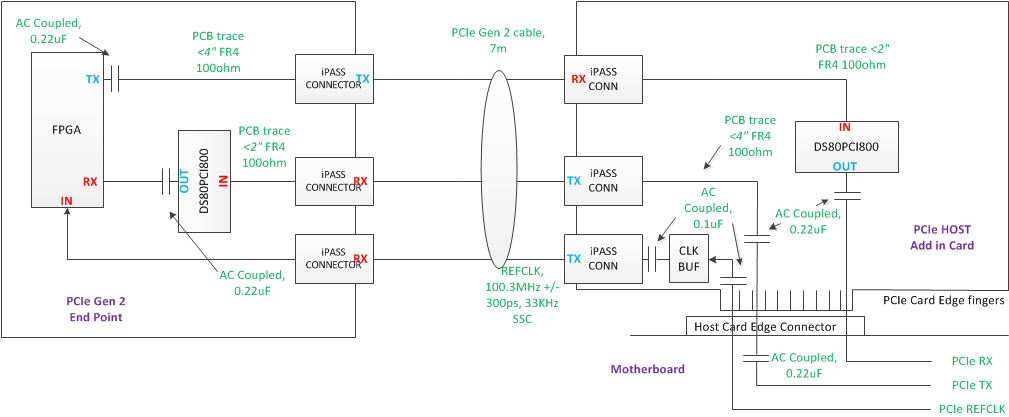

I am trying to model in webench a TX --> Cable --> DS80PCI810 --> RX. What is confusing is how is the insertion loss number provided? Do I have to add a -ve sign infront of the loss value? You can see in the picture attached, this doesn't produce any good output. But what I see in the app note is that losses of upto -40db are corrected by this part. So I am not sure what I'm missing in my sim?

I have been told that this part can get upto 10meter on a miniSAS HD cable over Gen 3 speeds. Looking at the miniSAS HD cable spec, I see that it has about -11dB insertion loss at 4GHz over 5m. And the PCIe Addin card loss budget is about 13.5dB. So 25dB doesn't seem that far fetched number.

I should mention, that I am not sure if I need to enter a negative value in the insertion loss field because the example or default value is given as a positive number and the graph looks correct as well with the positive value.