Hello,

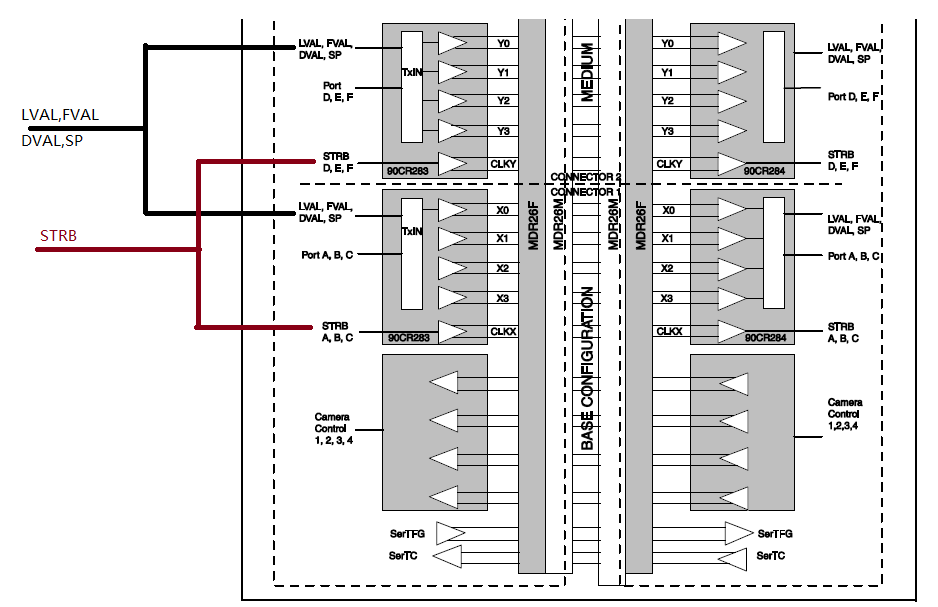

I'm confused about the enable signals(FVAL/LVAL/DVAL) of DS90CR287. I want use two DS90CR287 to implement a camera link medium interface, but I don't know if I can(or MUST?) connect the two enables signals to one source, and connect the two strb to one source, likes below:

thanks very much!