Other Parts Discussed in Thread: TLK1101E

Hi,

Can you please help clarify below issue for a customer?

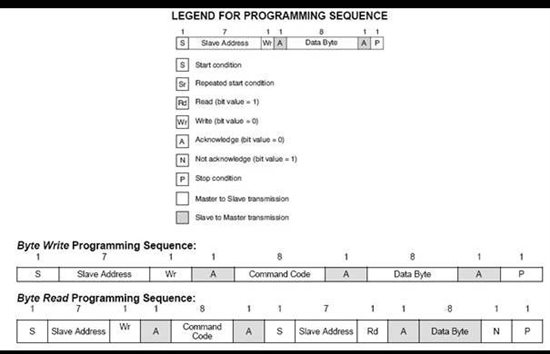

In setting functions from a uC to communicate through the I2C interface (ONET8501P and TLK1101E), they will each acknowledge their own slave address, but then will hold down SDA line for the following 8 bits. The SDA line is then released for the 9th or acknowledge bit sending a NAK. I am using the same function to shift out both the slave address byte and the register address byte where the problem occurs. I have measured the clock L-H periods, rise-fall times- data and stop time setups etc.. and everything looks well within specs. The SCL is running at 70KHz.