Hello,

we have a massive problem with our phys:

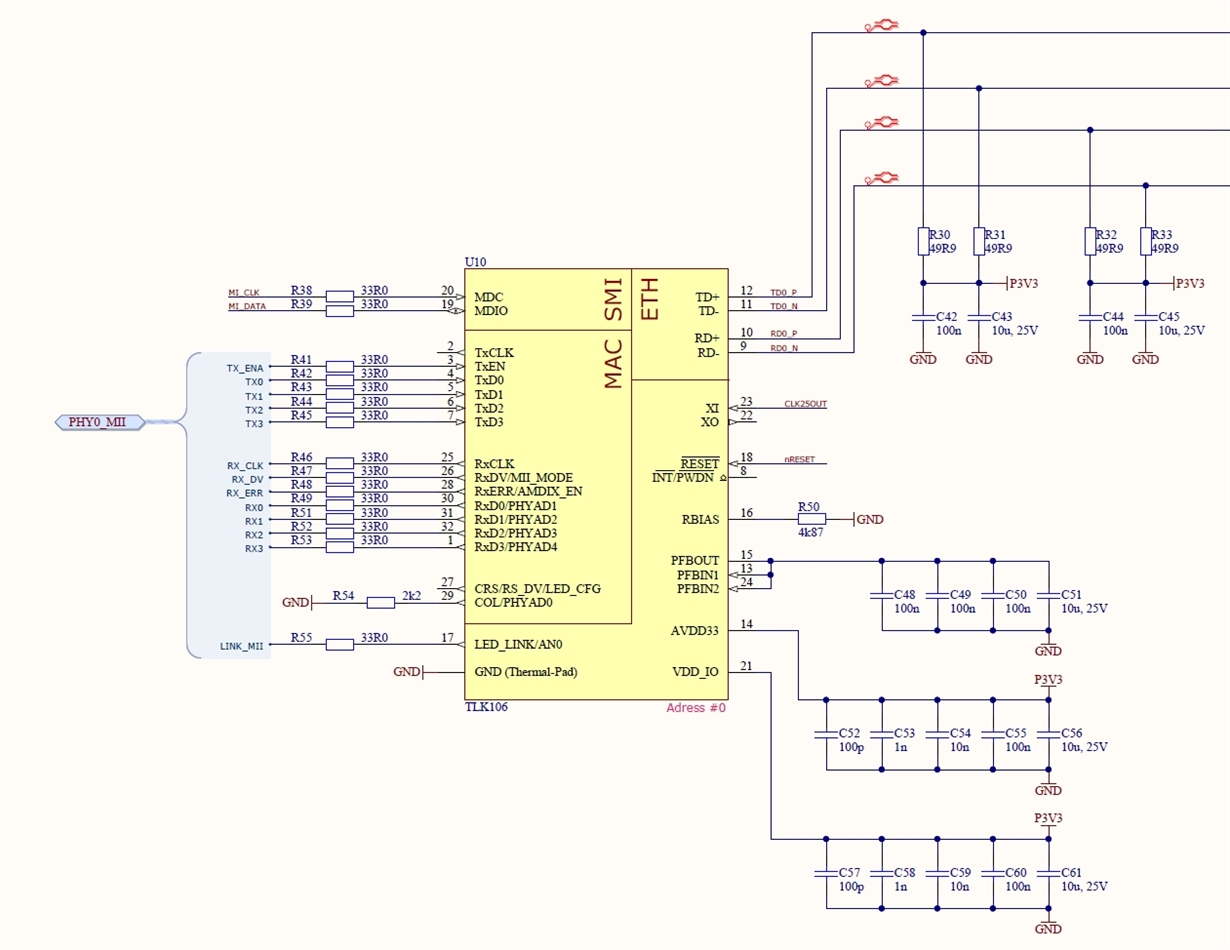

We use the phys TLK105 and 106 in 2 different applications, always in combination with a ET1100 Ethercat-slave-controller.

They run without problems up to Tc=90°C (Ta is about 10°C below) in the climate cabinet.

But if we restart a Board by a power-on, the phys stay completely dead at temperatures Tc above 40°C (TLK105) or Tc above 45°C (TLK106)

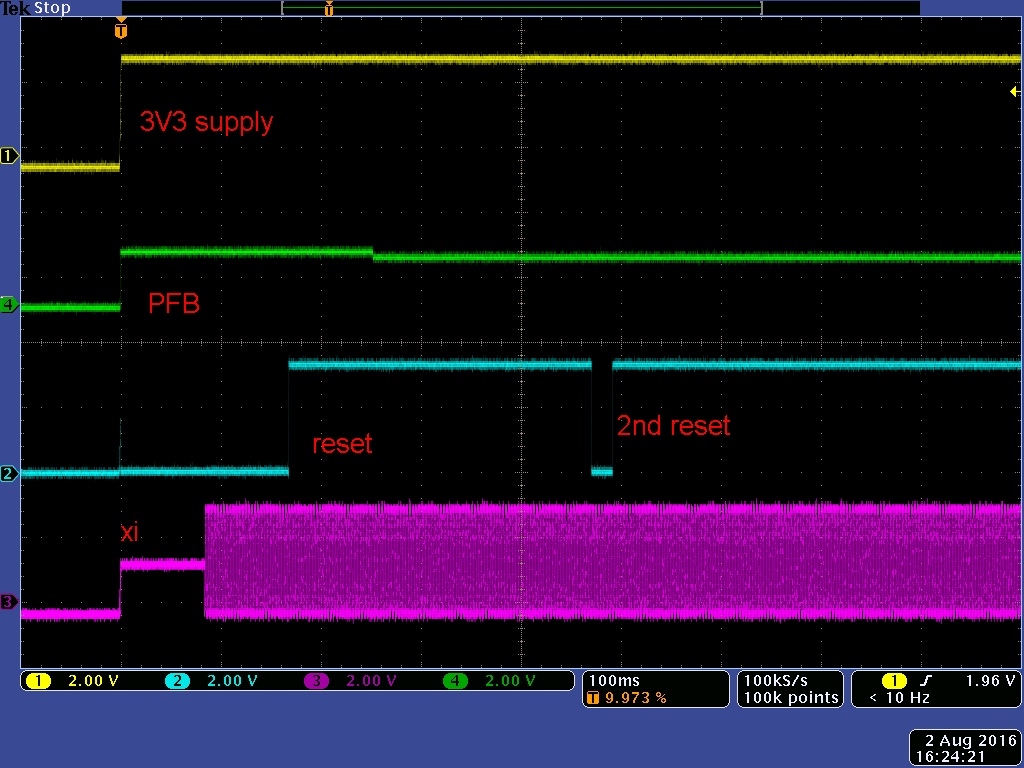

We found a workaround for this behaviour: if we activate 2sec after power on a 2nd resetpulse for some ms, the phys start working at all temperatures.

This effect is absolutely reproducible on different boards. We are sure that this is a problem of the phy, because if we warm up one phy of three selectively , then this port doesn't start at power-on, the others work well. The ET1100 is nonsensitive to higher temperatures.

The phys have single supply, 25MHz clk, the reset at start is ~ 180ms, the voltage at start rises in ~2ms to 3.3V,

Has anyone yet observed this strange behaviour or has a explanation for it ?

best regards

Karl