Hi,

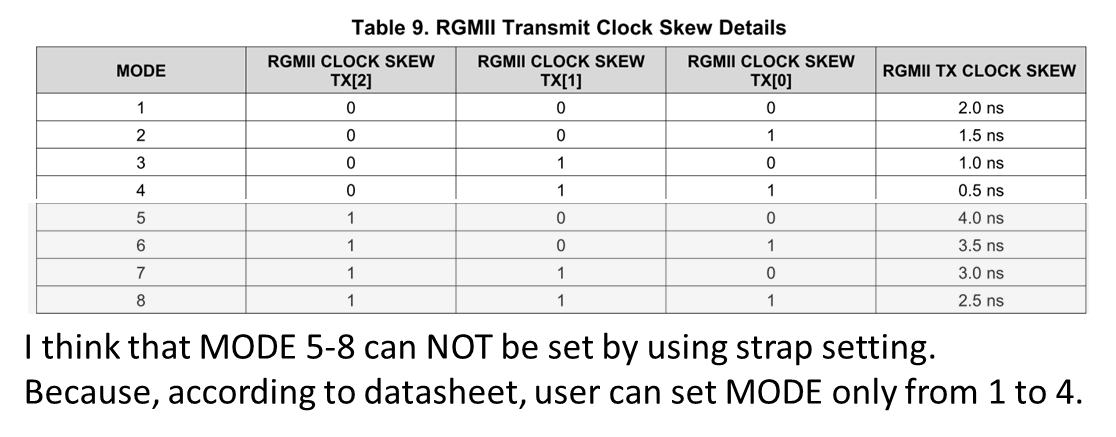

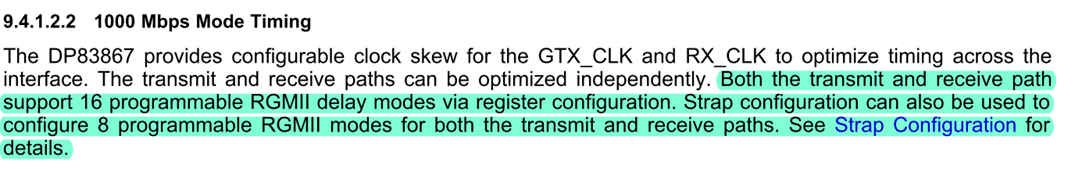

I understood that user can set delay setting by using following both two methods.

1. By using register (16 proggramable setting)

2. By using strap (8 proggramable setting)

And also, user need to set "RGMII_TX/RX_CLK_DELAY" bit to "1" to enable register setting.

However, my customer said that default setting of "RGMII_TX/RX_CLK_DELAY" was "1" (according to datasheet, default setting is "0").

I think that this may be incorrect infomation from customer, but if their confirmation is correct, this is bug of the device. So, could you please confirm default value of "RGMII_TX_CLK_DELAY" and "RGMII_RX_CLK_DELAY" bit just in case ?

Best Regards,

Machida