Other Parts Discussed in Thread: LMV614

Hello, using the TPL0102 i'm aiming to use the device in rheostat mode as a variable resistor. Specifically, as mentioned in Section 7.1, Page. 11 of the datasheet to combine both channels to achieve 512 settings between 0 Ohms and 200kOhms.

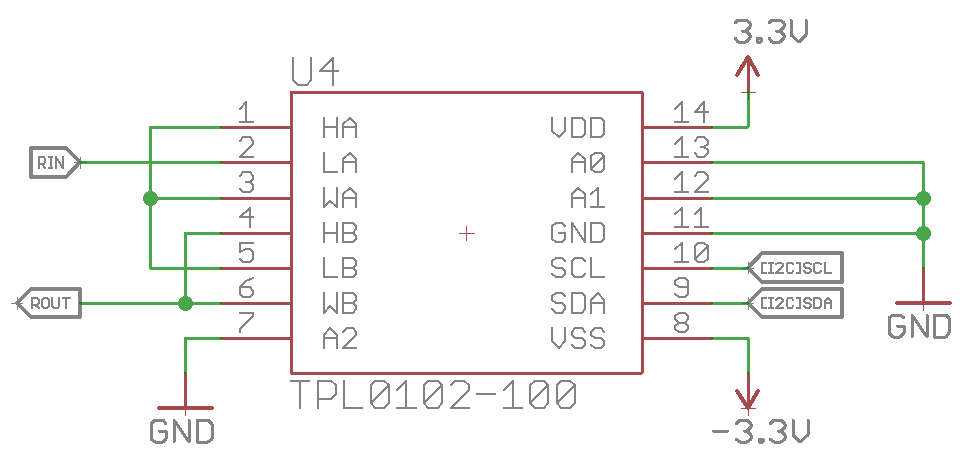

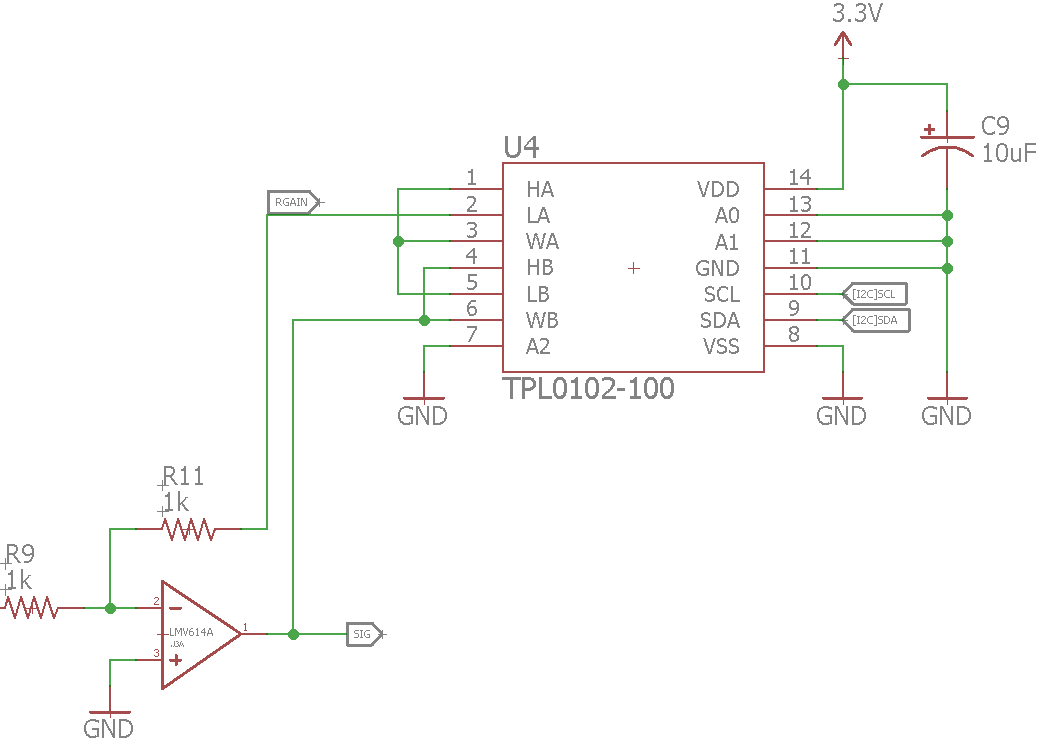

- I first wanted to verify that this was what is implied by that last paragraph where channel A is programmable between 0 - 100kOhms and B has the same capability and this is achieved by wiring the two channels in series?

- In Section 7.4.3, Page. 14, the datasheet mentions that in Rheostat mode, the W and H terminals can be tied together. Is this also true when both channels are combined as shown in my schematic below? Should I just leave the HA and HB floating?

My schematic is attached below and I would appreciate it if anyone could verify that it is wired correctly. As mentioned above, my intentions are that between Rin and Rout there is a programmable resistance between 0 and 200kOhms.