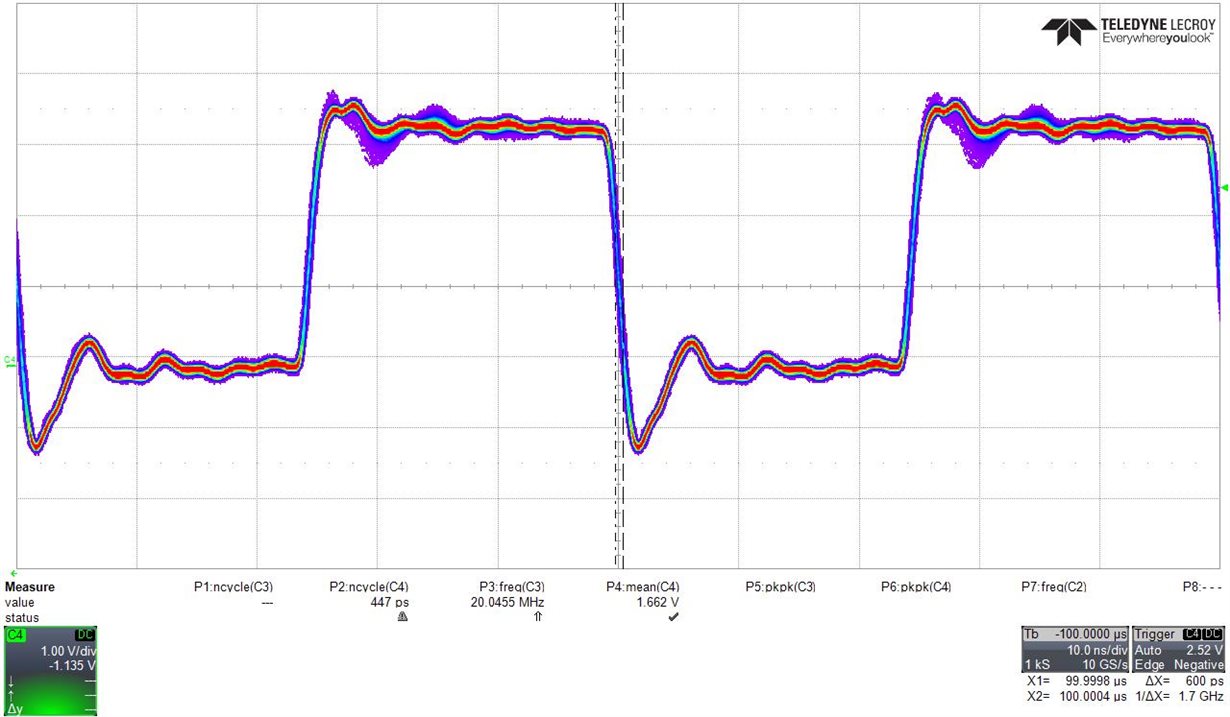

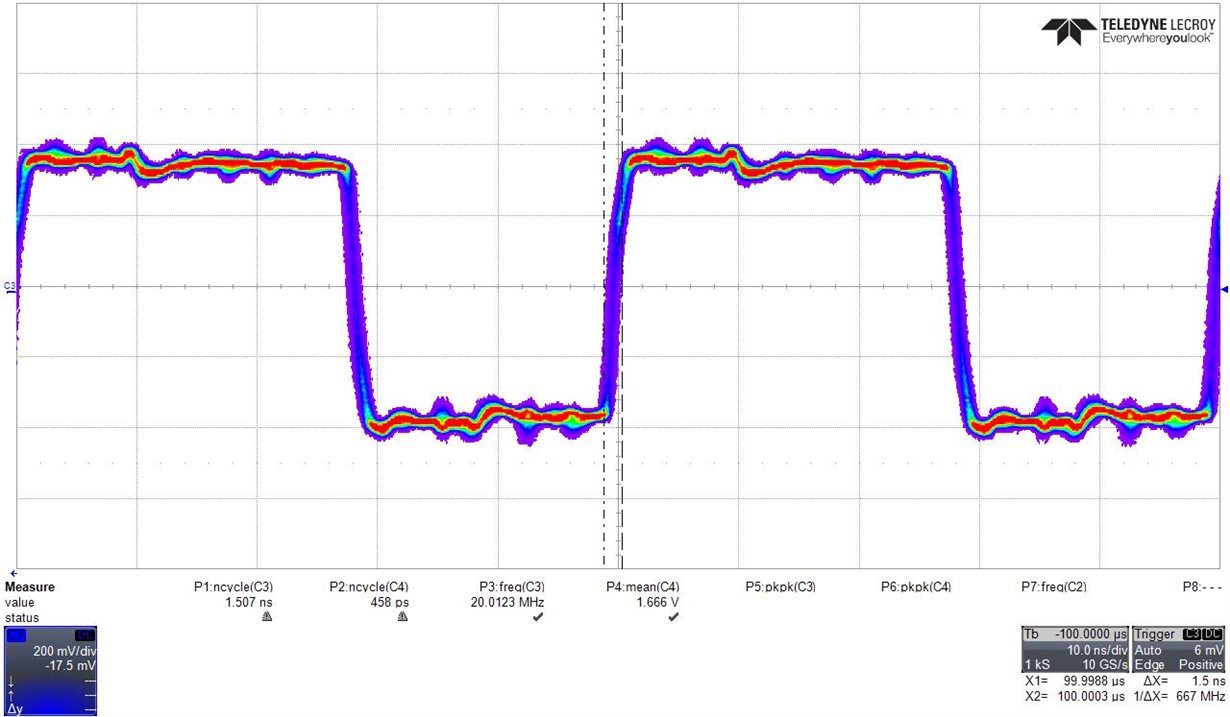

I'm working with a DS90CR287 chip and I am seeing dropped clock cycles on the output clock (TXCLKOUT) when running at 20MHz, which is the minimum spec'd clock frequency. There is significantly more jitter on the output clock than I would have expected (~2ns) considering the input clock is incredibly clean. This seems to be causing problems with one of our frame grabbers. Is there anything that would be causing the poor output clock?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.