Hello!

I'd like to ask you for some advice, what do you think is wrong with our setup.

We are using SN65DSI83 (DSI to LVDS) converter.

Our Panel / Connection specification is:

- 4 DSI data lanes + Clock (all 5 of them are diff. pairs)

- LVDS Panel (1280x800 pix resolution) (attached datasheet and Screenshot of DSI Tuner tool)

- Panel DE is positive polarity driven, HS and VS are both negative polarity driven.

- We are sure that we have working DSI signal on Clock and Data lanes (frequency at about 456MHz)

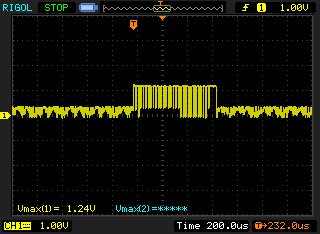

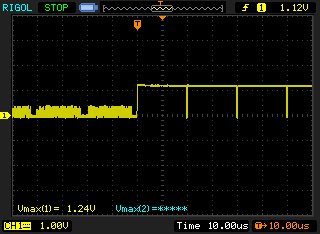

- We achieved to generate Test patern signal on our LCD (no errors bit set in SN65dsi83 error register (0xE5))

- DSI video has 24bpp, and SN65DSI83 is set to change it in 18bpp video.

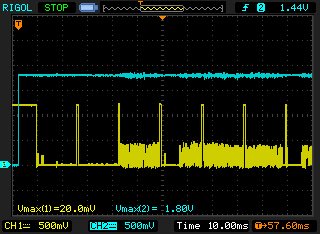

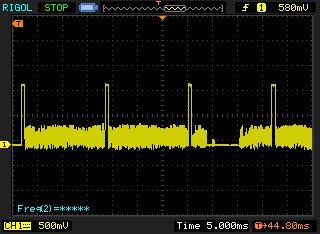

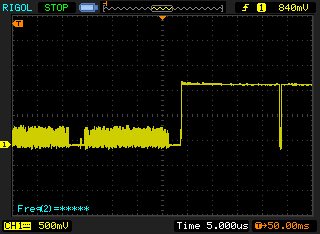

- When we turn off Test patern generation feature, we also don't have any error bits set in error register (All bits has zero value) But we still don't have picture on on our panel. LVDS clock looks good, at frequency around 75MHz. What is strange is that signal on Data lane 2 (diff pair) has similar signal as clock lane. On data lane 0 and 1, there is no signal. We have impedance/lenght matched differential pair lanes, with good spacing between them. Hardware shoudn't be problematic.

What do you recommend that we should try and change?