Hi,

We have problems to operate 1GbE retimer, because probably the simple setting, according to the DS, is not working or is missing some configuration.

DS 7.3.12

write reg 0x09 (bit 5) = 1

write reg 0x1E (bit7:5) = "000"

The 1GbE external testset is not receiving any data from retimer.

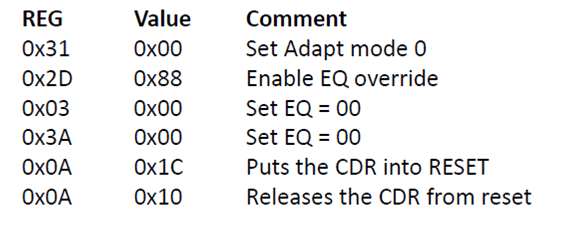

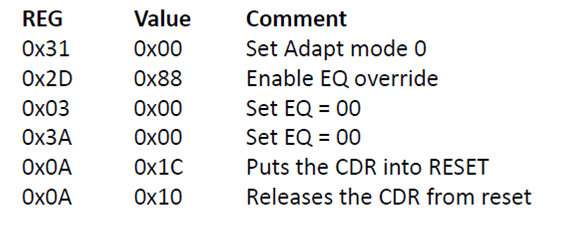

I already applied the configs (commands below) of the "DF410 Support for 2.5G Ethernet" discussion, but is not working:

Reg 0xFF = 0x0C //Access channel registers

Reg 0x2F[7:4] = 1100'b // Set lock rate for Interlaaken-2 (10.3125 Gbps with Divide-by-1 VCO divider only)

Reg 0x1E[7:5] = 000'b // Output raw data if CDR is not locked

Reg 0x3F[7] = 1'b //This is a reserved bit that must be set to ensure appropriate raw data is output

Thanks,

Érico Sawabe

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.