Hi dear supporting team,

when the PC send data to DP83848, then connect to FPGA, the data could be received normally. inside FPGA, customer made a ARP+UDP internet access data sending receiving program. and also reply the requested data package to DP83848 TXD[3:0]. TXCLK and TXEN. at DP83848 customer could use scope to capture the signal, while when signal get to DP83848, they could not get signal at DIFF output.

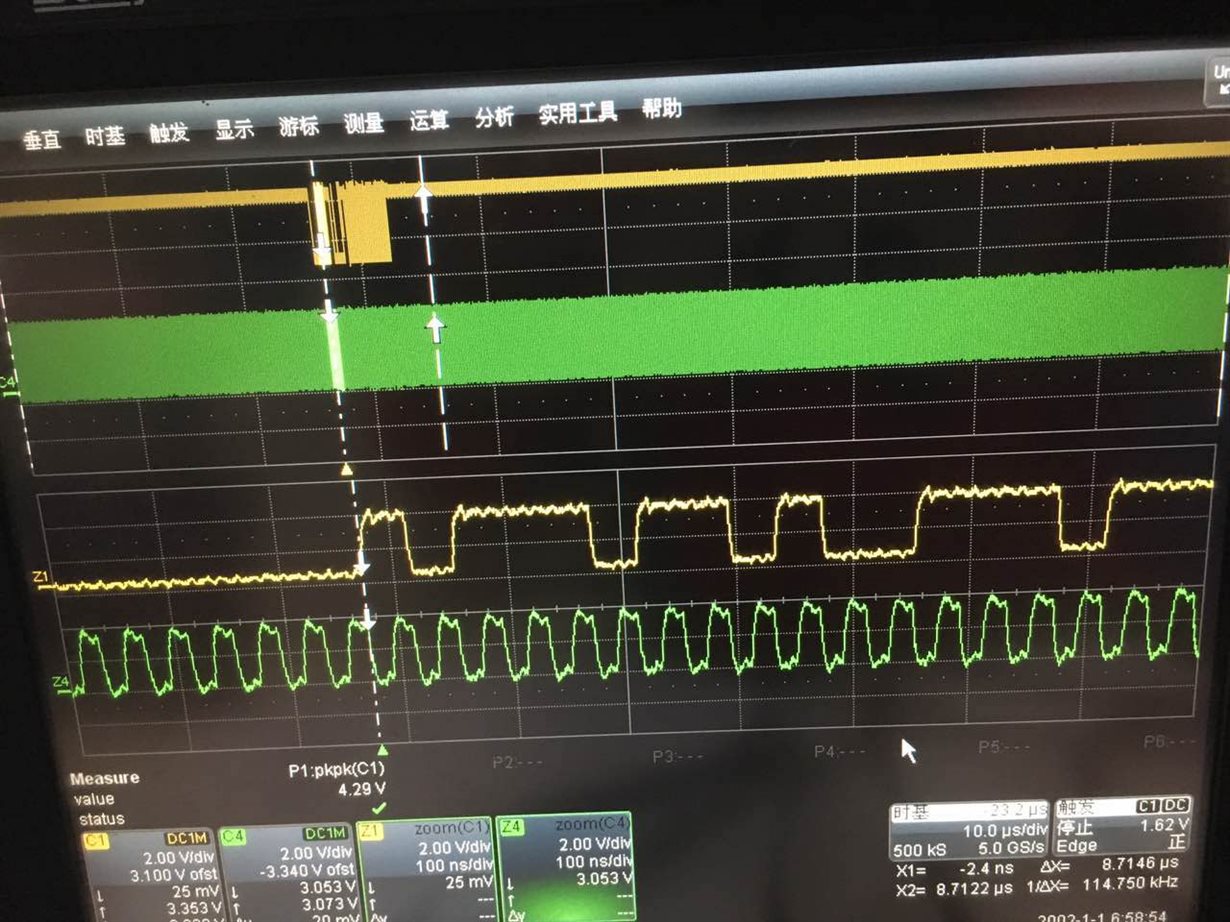

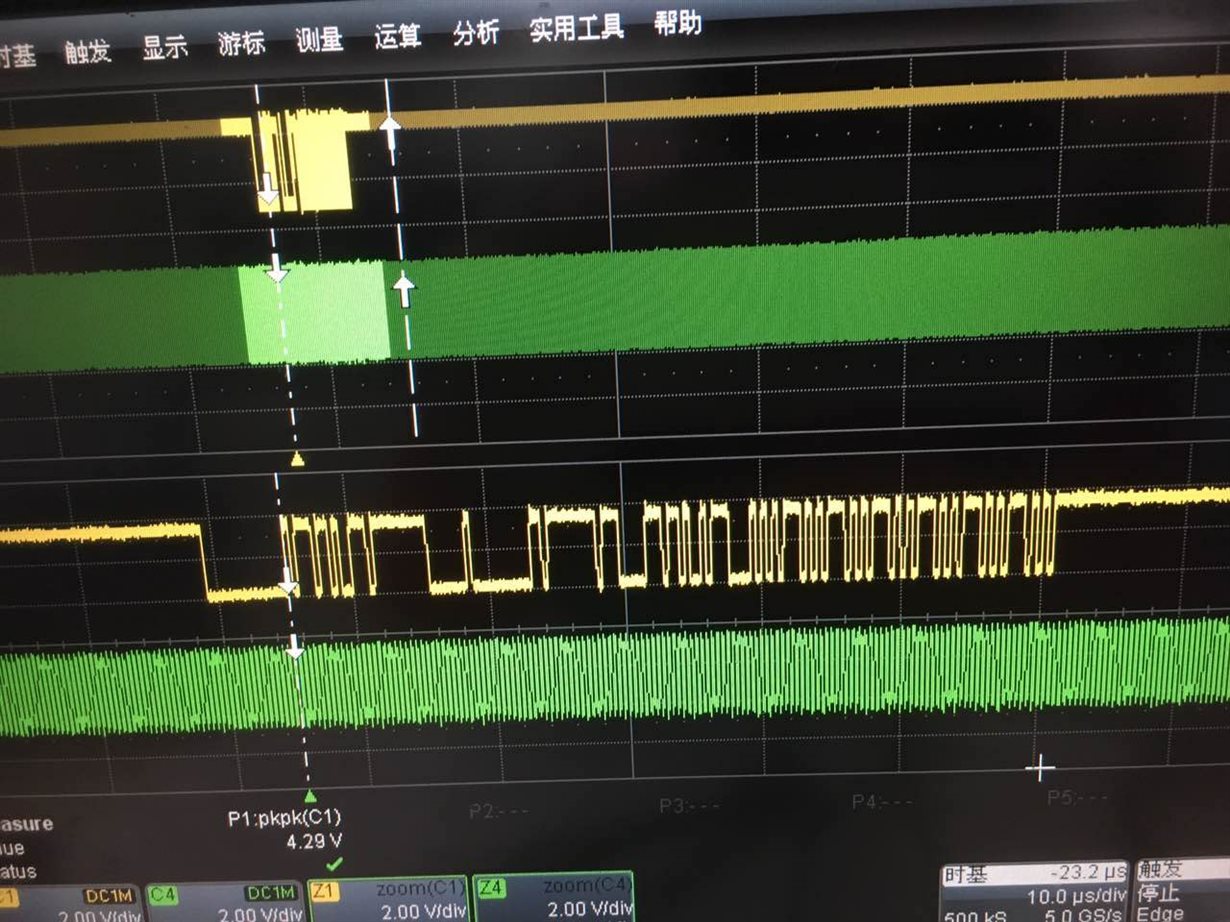

1. TXD signal and the CLK signal is as below, it seems align with the TX timing in the d/s.

2. during debugging, customer did not use MDIO and MDC, customer just do hardware reset, and did not do s/w reset, is it ok?