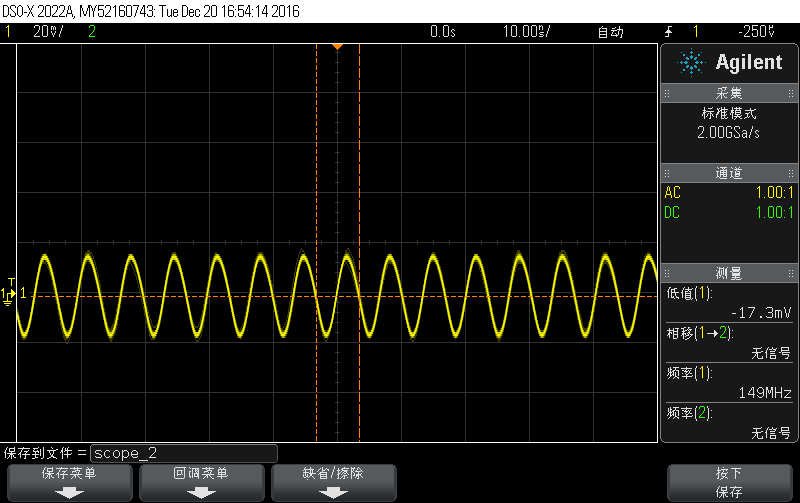

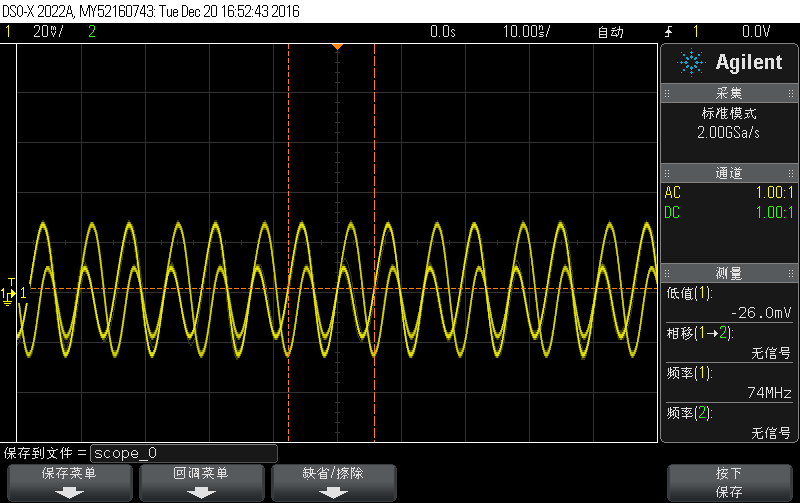

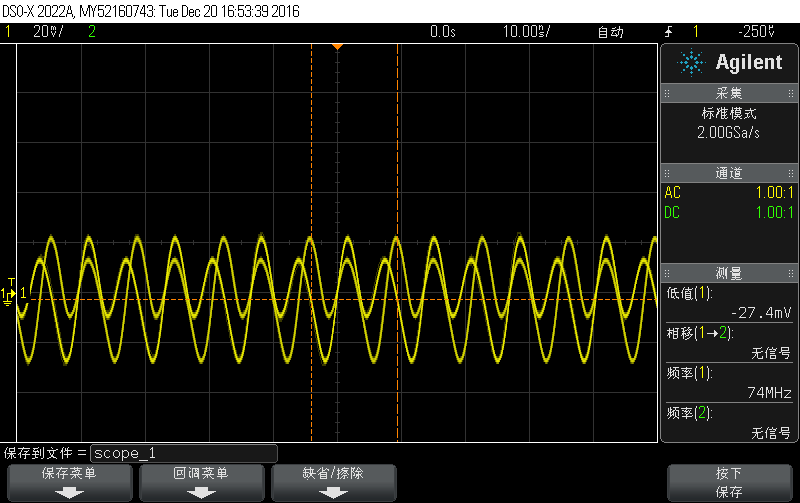

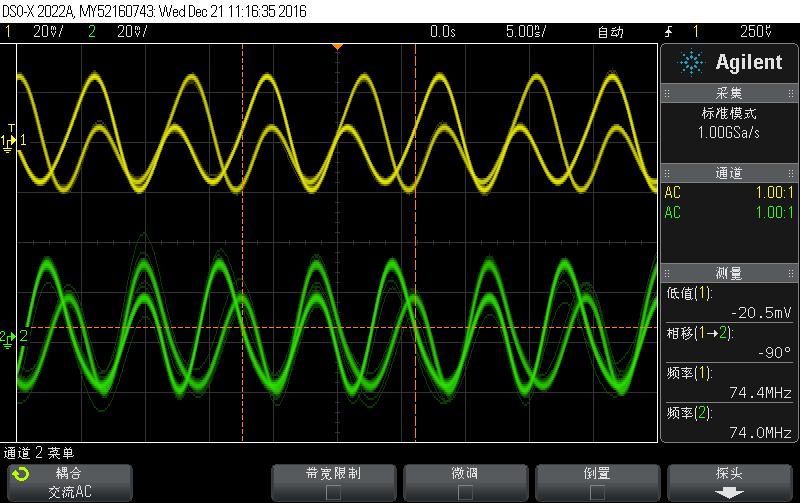

Occasionally, the output of 148.35MHz port (Pin 23 & 24) fails after power up, by channce of around 3/20. The waveform measured then looks wierd as below snapshot (P/N). However, the 148.5MHz port always works fine.

Currently, there is no any configuration for LMH1983. It always boots up with default values, expecting to lock to the input reference (F/V/H and they could be all tied to low or some non-supported format) and generate apporpriate 148.5MHz clock and 148.35MHz clock. What could be the reason for this? And should I have to configure some registers to recover it?

The below snapshots are good 148.35MHz, bad 148.35MHz of P port, bad 148.35MHz of N port. Thank you.