Part Number: DP83867IS

Hi Team,

I found SPEED SELECTION LSB/MSB in Basic Mode Control Register (BMCR) as the following.

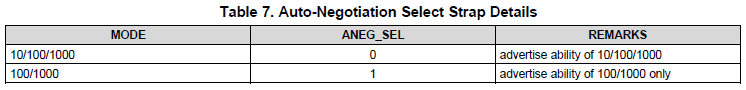

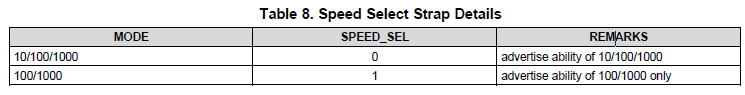

Does it correspond to the following SPEED_SEL in Strap Configuration?

I wonder why only two mode(10/100/1000 or 100/1000) are prepared in strap configuration while 10 or 100 or 1000 can be selected in Basic Mode Control Register.

I don't have a detailed knowledge about ethernet, so your advice would be appreciated.

Best Regards,

Yaita / Japan disty