Part Number: PCA9306

Hello team,

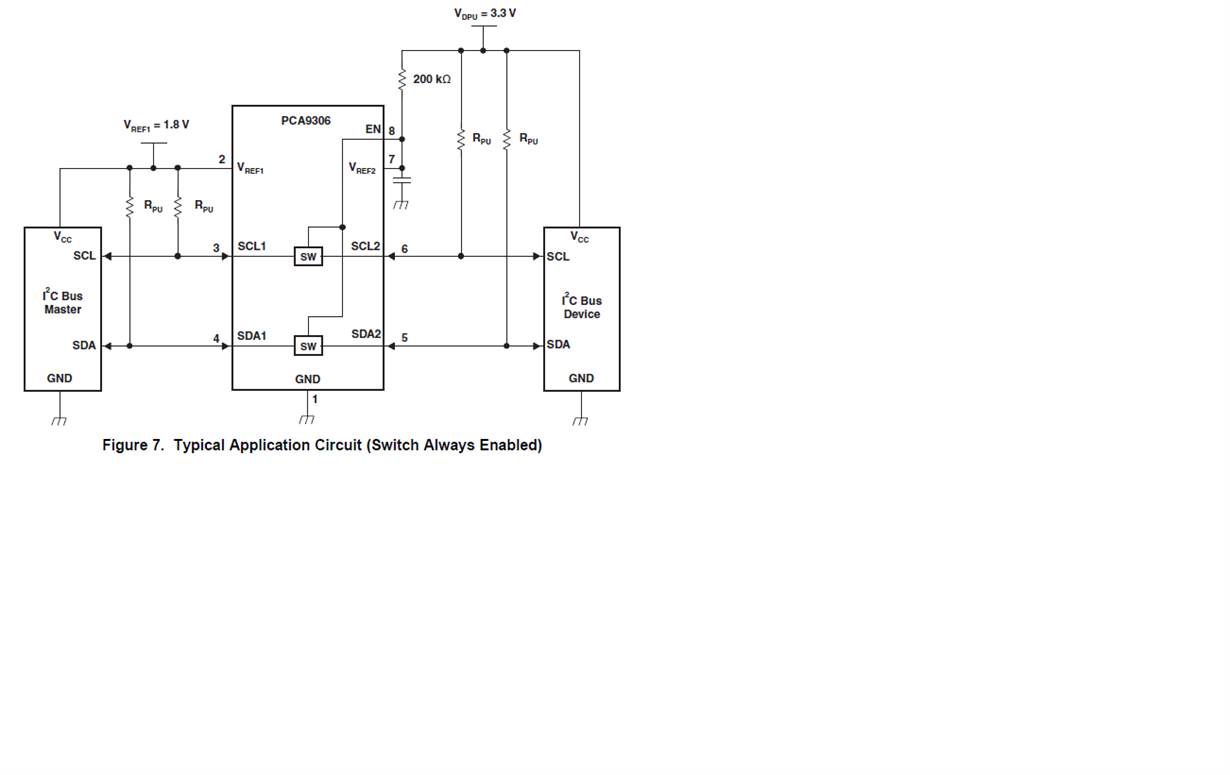

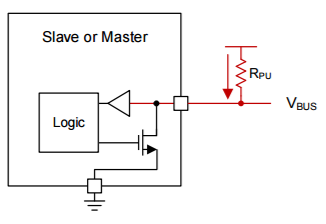

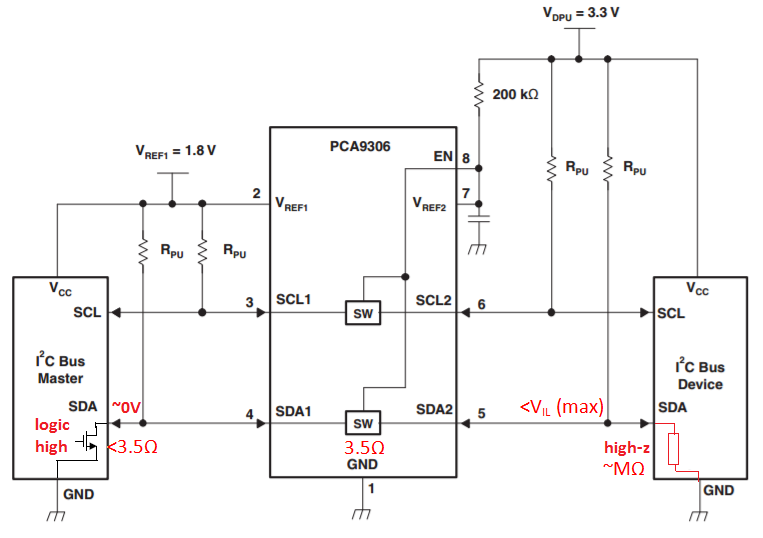

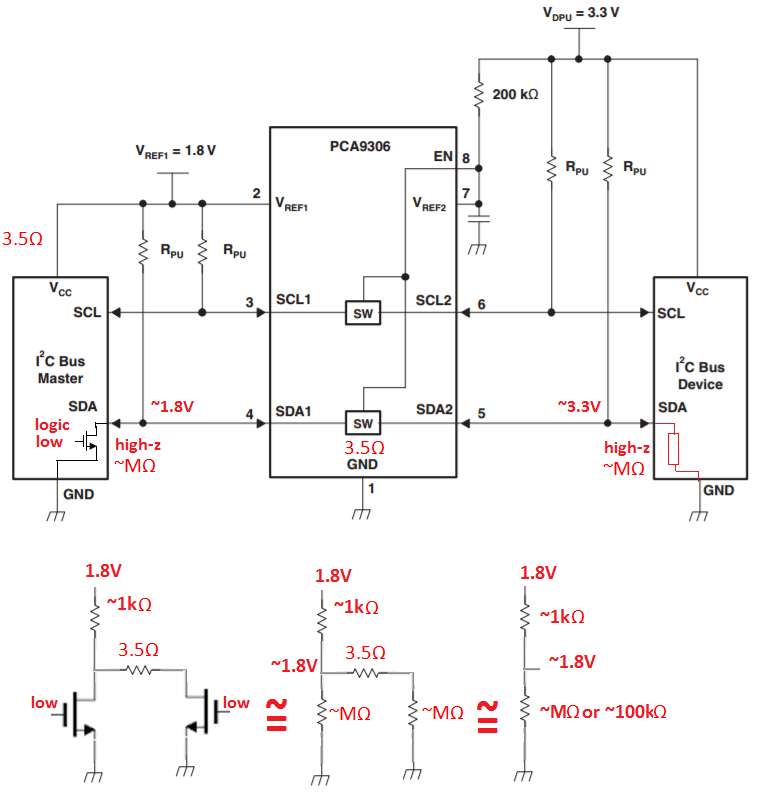

Below is PCA9306 typical application, switch is always enabled.If the signal transfer from 1.8V side to 3.3V side, when there is 1.8V high level input signal, you know the Ron of our part is about 3.5ohm, so there is 3.5ohm+ Rpu resistor between 1.8V and 3.3V, because the Ron of our part is very small, so the voltage of output of 3.3V side should be very close to 1.8V level, so how does the output transfer to 3.3V level?

1. For this application, the switch should be always enabled, and the Ron is about 3.5ohm all the time, correct?

Regards,

nanfang