[ PCA9306 ] Support Clock Stretching? and Power Sequence

Hi there,

Do I need to consider whether PCA9306 support the clock stretching or not?

My customer would use PCA9306 for their design which need to support the clock stretching.

Should I suggest customer to use other device with clock stretching support?

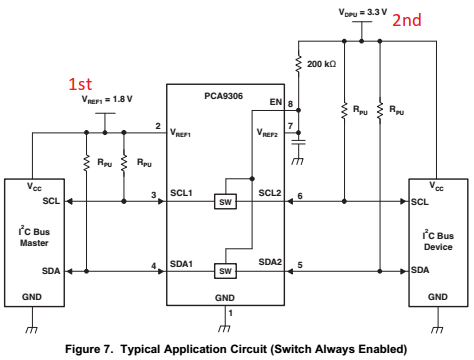

Also, in my customer system (similar to Fig. 7 below), Vref1=1.8V ramp up first (before Vdpu=3.3V ramp).

When Vref1=1.8V is powered-on and Vdpu=3.3V is off, it's assumed that EN is high-z state.

Do you think that this situation cause any of problem?

My customer is concerned that the unexpected voltage is appeared on Vdpu side through PCA9306.

Thank you for your support in advance.

Regards,

Ken