Part Number: DS92LV18

Hello

I am investigating an issue with the DS90LV18 Serializer/Deserializer chipset.

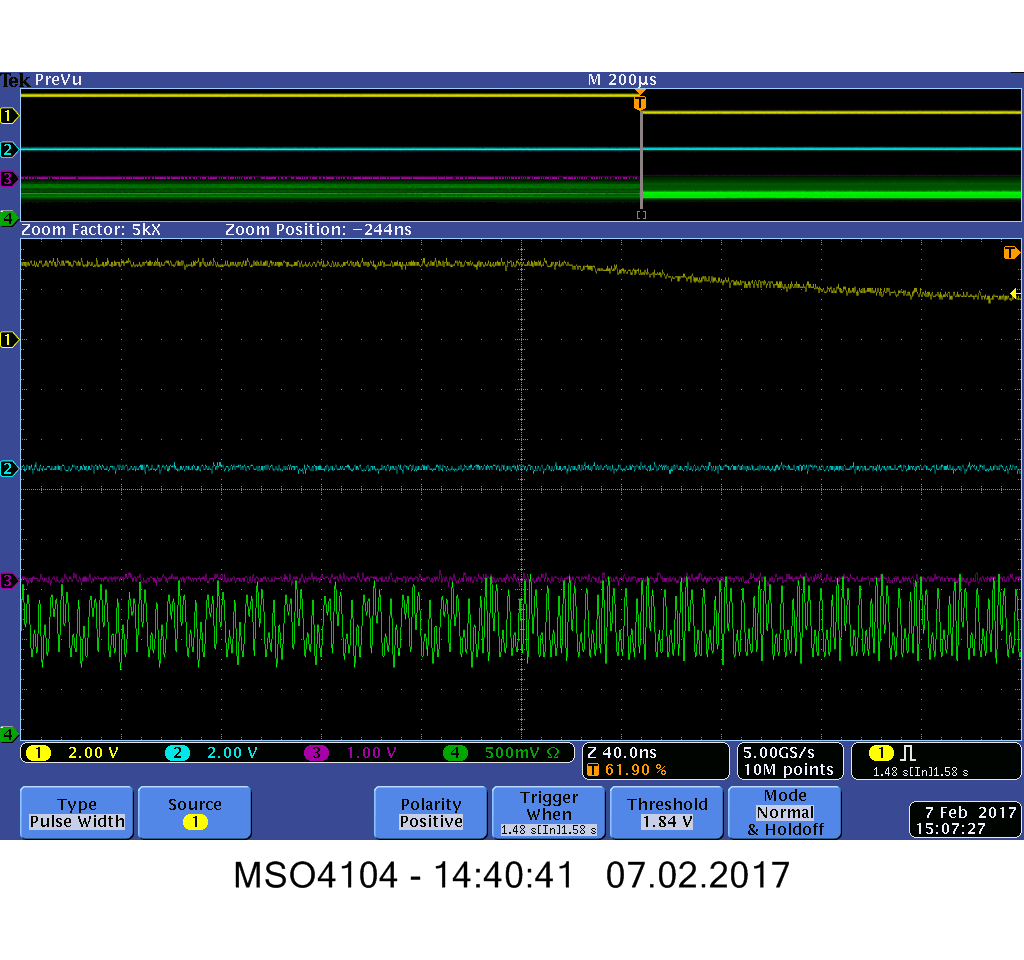

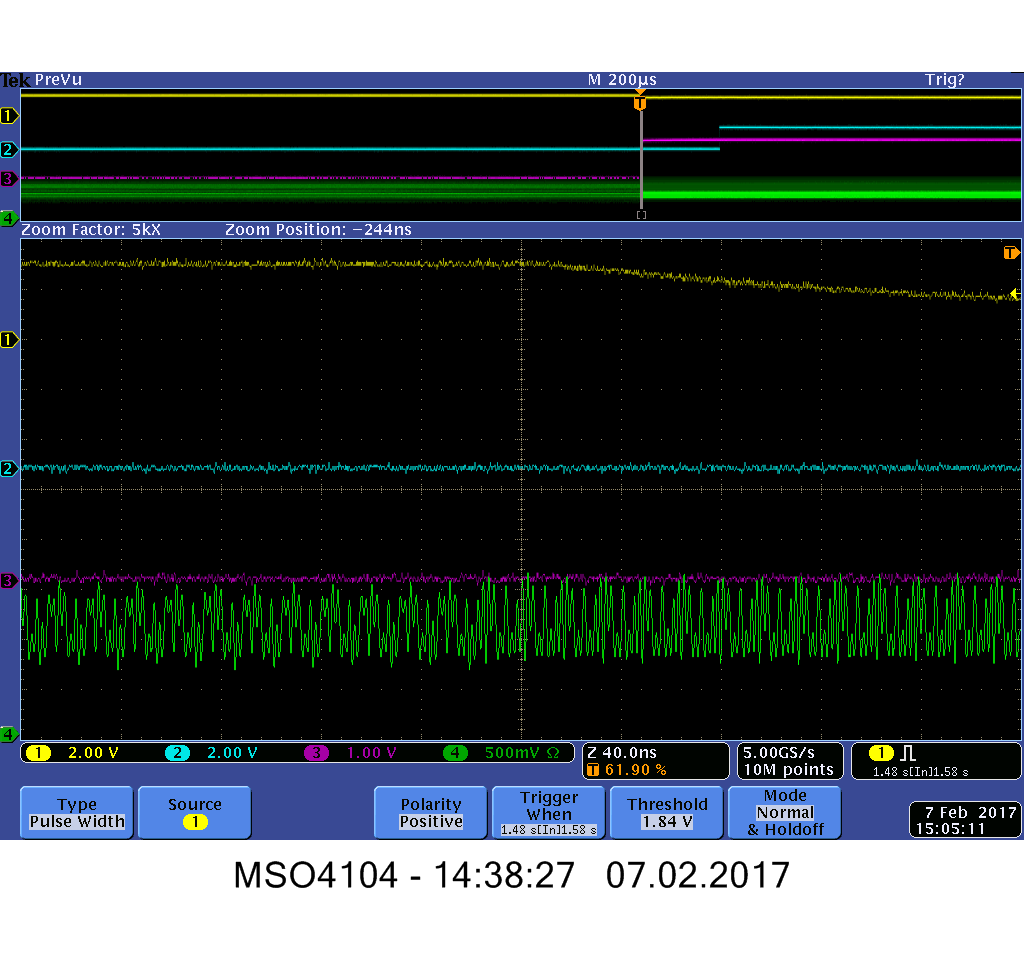

In order to establish the link between Serializer and Deserializer I assert the Serializer SYNC input (pin 20) for about 50ms. As you can see in the attached scope image the PLL of the Deserializer locks (channel #3 goes low). Most of the time the data transfer now works properly (good case). But, about every 40th time the PLL loses the lock (channel #3 goes high) when the very first data packet is sent (spike of channel #1).

After about 15ms the PLL locks again and it seems the link works from now on. I do not understand why the PLL unlocks sometimes. It seems to me that although the PLL lock signal goes low the PLL is not properly locked (e.g. locked to the wrong edge?) and when receiving the first data packet the PLL "realizes" that something is wrong and loses lock.

My questions:

1. What could be the root cause that the PLL unlocks for a short time?

2. Has anyone seen this behavior too?

3. As mentioned, I assert the SYNC input for ~50ms. According to the datasheet this should be by far long enough for the PLL to lock. However, do I have to send the SYNPAT for a longer time?

4. Is there a better way for establishing the link then sending only the SYNCPAT (e.g. alternating SYNCPAT with random data)?

Description of scope channels:

CH1: Deserializer ROUT0 (pin 45)

CH3: Deserializer /LOCK (pin 63)

CH2&4: not of interest for this question

Good case:

Error case: