Part Number: TUSB2046B

Other Parts Discussed in Thread: TUSB3410

I'd like to ask about TUSB2046B reset condition. TUSB2046B datasheet says followings.

"Generally, a reset with a pulse width between 100 μs and 1 ms is recommended after 3.3-V VCC reaches its 90%. Clock signal has to be active during the last 60 μs of the reset window."

And, SLLA314 Says followings,

"Texas Instruments recommends a minimum of 100 µs to a maximum of 1 ms of reset timing. If the hub is held in reset for a longer period of time, it can fail to respond promptly to USB host signaling and not complete enumeration. This is typically an issue with embedded system applications."

It seems that the reset window is decided for stable enumeration.

My question is, If we can control external 1.5kohm pull-up register on DP, is it possible to extend the time of reset window?

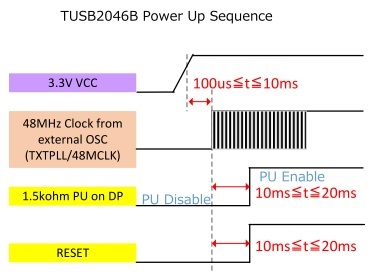

Is following sequence acceptable?