Other Parts Discussed in Thread: DS125MB203, , DS100MB203

I all,

I'm in trouble with the DS125DF1610 device, this device is part of a complex design in which is also present a DS125MB203 chip.

I'm trying to configure del following loopback path toward an onboard FPGA:

FPGA (PRBS source) -> (3inch) -> DS100MB203 -> (7inch) -> (CH0 A RX) DS125DF1610 ->(CH0 A TX)DS125DF1610 -> (7inch) -> DS100MB203 -> (3inch) -> FPGA (PRBS ck)

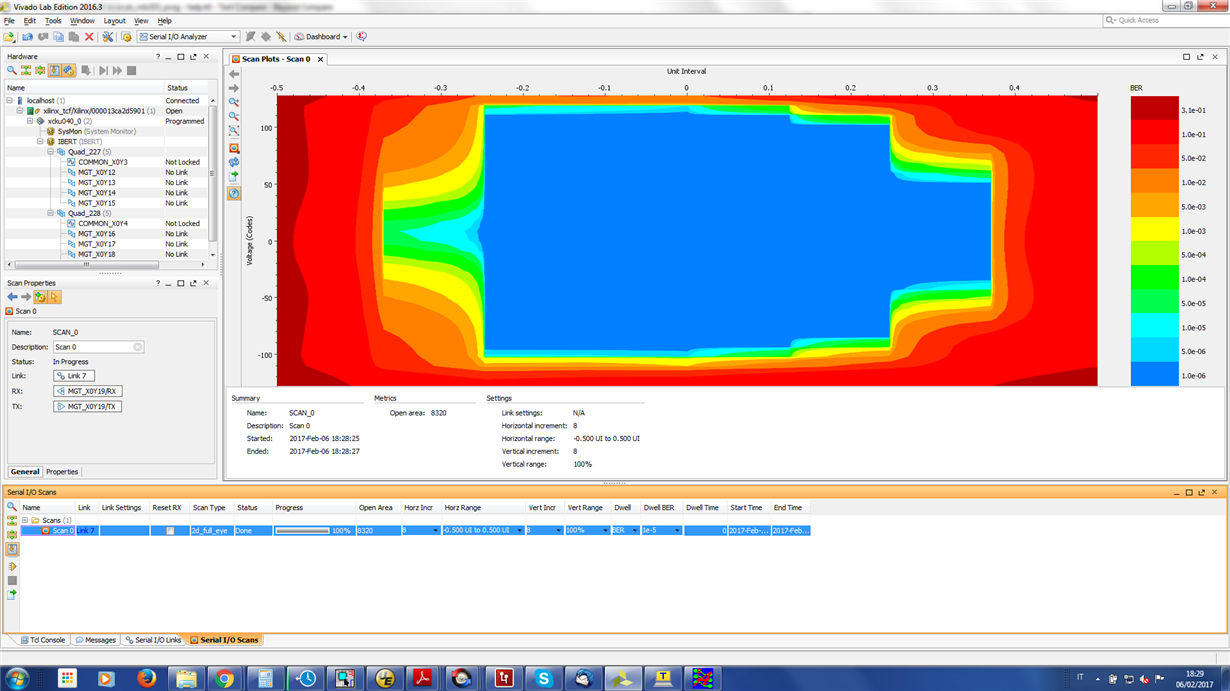

The final rate will be 12.5G CPRI, to make the setup easy I tryed a 4.9G CPRI rate, in this conditions I'm able to perform the PRBS check without problem, but I'm not able to see the CDR lock bit 4 in reg 0x78 up. The PRBS don't see any error, instead the DS125DF1610 reports a DFE_EQ_ERROR_NO_LOCK.

I'm not able to overcome this error also changing the adaptation, someone can help me?

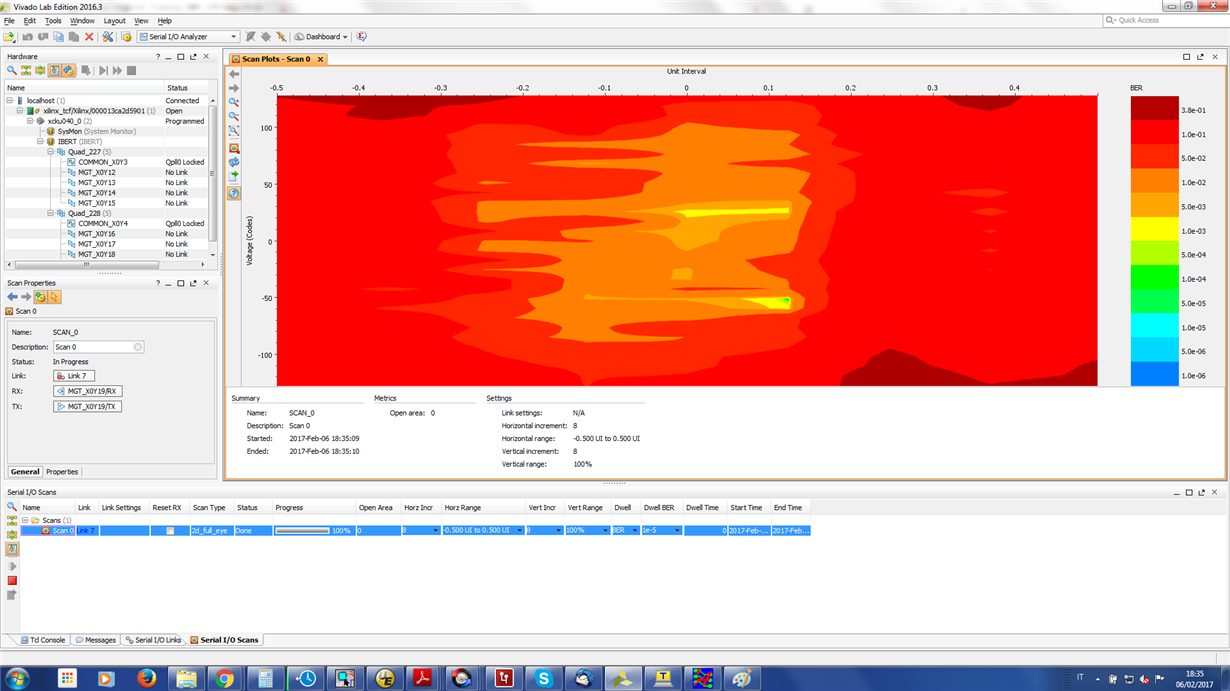

If I try the same configuration with an upper rate 9.8 I'm not able to perform any test, and the eye of incoming signal is totaly corrupted (instead at 4.9 seems perfect).

Tests made with the following setup (readback from device):

Shared

REG[0x00] = 0x00

REG[0x01] = 0x71

REG[0x02] = 0x00

REG[0x03] = 0x00

REG[0x04] = 0x01

REG[0x05] = 0x08

REG[0x06] = 0x00

REG[0x07] = 0x00

REG[0x08] = 0x00

REG[0x09] = 0x00

REG[0x0A] = 0x01

REG[0x0B] = 0x40

REG[0x0C] = 0x00

REG[0x0D] = 0x41

REG[0x0E] = 0x01

REG[0x0F] = 0xFF

REG[0x10] = 0xFF

REG[0x11] = 0x00

channel 0

REG[0x00] = 0x00

REG[0x01] = 0x80

REG[0x02] = 0x84

REG[0x03] = 0x00

REG[0x04] = 0x01

REG[0x05] = 0x01

REG[0x06] = 0x01

REG[0x07] = 0x01

REG[0x08] = 0x60

REG[0x09] = 0x20

REG[0x0A] = 0x50

REG[0x0B] = 0x6F

REG[0x0C] = 0x08

REG[0x0D] = 0xB4

REG[0x0E] = 0x93

REG[0x0F] = 0x69

REG[0x10] = 0x3A

REG[0x11] = 0x20

REG[0x12] = 0x60

REG[0x13] = 0x90

REG[0x14] = 0x00

REG[0x15] = 0x10

REG[0x16] = 0x7A

REG[0x17] = 0x25

REG[0x18] = 0x40

REG[0x19] = 0x20

REG[0x1A] = 0xA0

REG[0x1B] = 0x03

REG[0x1C] = 0x90

REG[0x1D] = 0x00

REG[0x1E] = 0x21

REG[0x1F] = 0x55

REG[0x20] = 0x00

REG[0x21] = 0x00

REG[0x22] = 0x00

REG[0x23] = 0x02

REG[0x24] = 0x43

REG[0x25] = 0x00

REG[0x26] = 0x00

REG[0x27] = 0x00

REG[0x28] = 0x00

REG[0x29] = 0x00

REG[0x2A] = 0x00

REG[0x2B] = 0x0F

REG[0x2C] = 0xF2

REG[0x2D] = 0x07

REG[0x2E] = 0x00

REG[0x2F] = 0x86

REG[0x30] = 0x08

REG[0x31] = 0x43

REG[0x32] = 0x11

REG[0x33] = 0x88

REG[0x34] = 0x3F

REG[0x35] = 0x1F

REG[0x36] = 0x30

REG[0x37] = 0x00

REG[0x38] = 0x10

REG[0x39] = 0x00

REG[0x3A] = 0x00

REG[0x3B] = 0x31

REG[0x3C] = 0x25

REG[0x3D] = 0x38

REG[0x3E] = 0x00

REG[0x3F] = 0xC4

REG[0x40] = 0x00

REG[0x41] = 0x01

REG[0x42] = 0x04

REG[0x43] = 0x10

REG[0x44] = 0x40

REG[0x45] = 0x08

REG[0x46] = 0x02

REG[0x47] = 0x80

REG[0x48] = 0x03

REG[0x49] = 0x0C

REG[0x4A] = 0x30

REG[0x4B] = 0x41

REG[0x4C] = 0x50

REG[0x4D] = 0xC0

REG[0x4E] = 0x60

REG[0x4F] = 0x90

REG[0x50] = 0x88

REG[0x51] = 0x82

REG[0x52] = 0xA0

REG[0x53] = 0x46

REG[0x54] = 0x52

REG[0x55] = 0x8C

REG[0x56] = 0xB0

REG[0x57] = 0xC8

REG[0x58] = 0x57

REG[0x59] = 0x5D

REG[0x5A] = 0x69

REG[0x5B] = 0x75

REG[0x5C] = 0xD5

REG[0x5D] = 0x99

REG[0x5E] = 0x96

REG[0x5F] = 0xA5

REG[0x60] = 0xB0

REG[0x61] = 0x02

REG[0x62] = 0xB0

REG[0x63] = 0x02

REG[0x64] = 0xDD

REG[0x65] = 0x00

REG[0x66] = 0x00

REG[0x67] = 0x20

REG[0x68] = 0x00

REG[0x69] = 0x0A

REG[0x6A] = 0x22

REG[0x6B] = 0x20

REG[0x6C] = 0x20

REG[0x6D] = 0x20

REG[0x6E] = 0x00

REG[0x6F] = 0x00

REG[0x70] = 0x03

REG[0x71] = 0x00

REG[0x72] = 0x00

REG[0x73] = 0x00

REG[0x74] = 0x00

REG[0x75] = 0x00

REG[0x76] = 0x22

REG[0x77] = 0x1A

REG[0x78] = 0x20

REG[0x79] = 0x13

REG[0x7A] = 0x00

REG[0x7B] = 0x00

REG[0x7C] = 0x00

REG[0x7D] = 0x44

REG[0x7E] = 0x83

REG[0x7F] = 0x2A

REG[0x80] = 0x00

REG[0x81] = 0x00

REG[0x82] = 0x00

REG[0x83] = 0x00

REG[0x84] = 0x00

REG[0x85] = 0x00

REG[0x86] = 0x20

REG[0x87] = 0xA6

REG[0x88] = 0x0C

REG[0x89] = 0x00

REG[0x8A] = 0x00

REG[0x8B] = 0x00

REG[0x8C] = 0x00

REG[0x8D] = 0x06

REG[0x8E] = 0x1C

REG[0x8F] = 0x00

REG[0x90] = 0x00

REG[0x91] = 0x00

REG[0x92] = 0x00

REG[0x93] = 0x00

REG[0x94] = 0x00

REG[0x95] = 0x00

REG[0x96] = 0x1C

REG[0x97] = 0x00

REG[0x98] = 0xC0

REG[0x99] = 0x3F

REG[0x9A] = 0x3F

REG[0x9B] = 0x00

Thanks

Maxx