Hi E2E members,

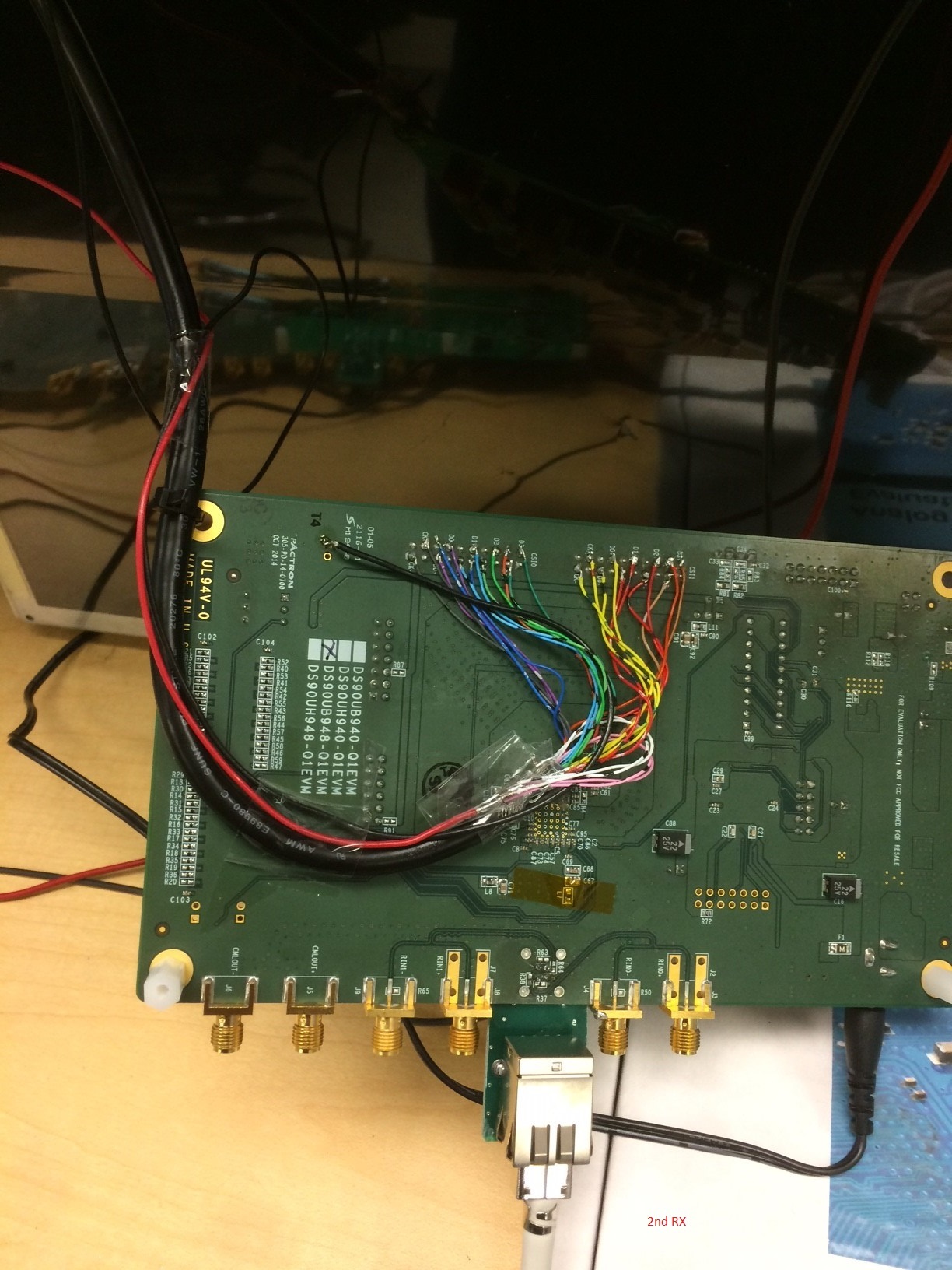

I got link-3 parts, 947 and 948 EVM, connected and it works fine. No hop.

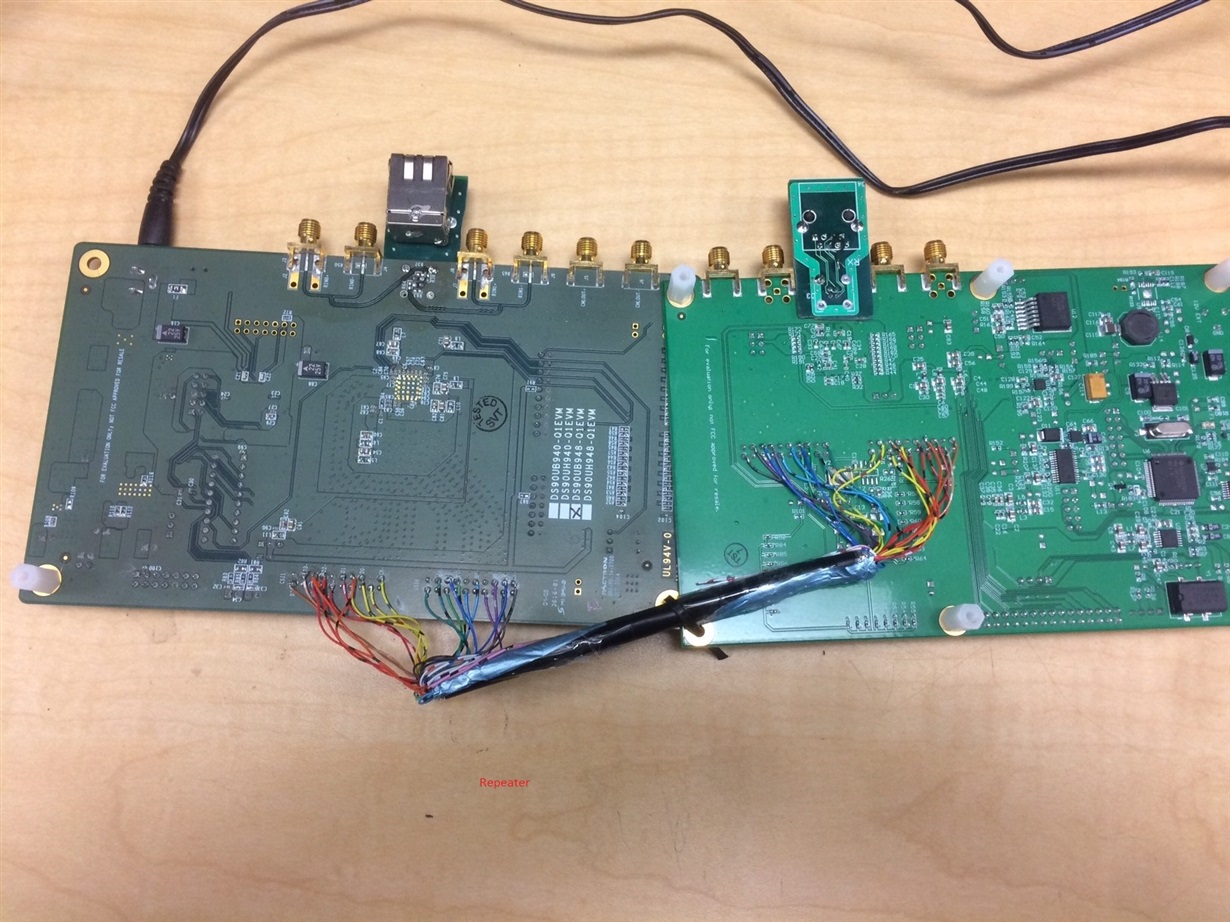

In my application I need 1 hop so I add one more 947/948 in the middle.

It doesn't lock well. It seems the jitter accumulate. Is there any app note to describe how to play with the jitter and pll loop bandwidth?

Many many Thanks.

Mike