Hello There

I would like to clarify some information from the datasheet if possible.

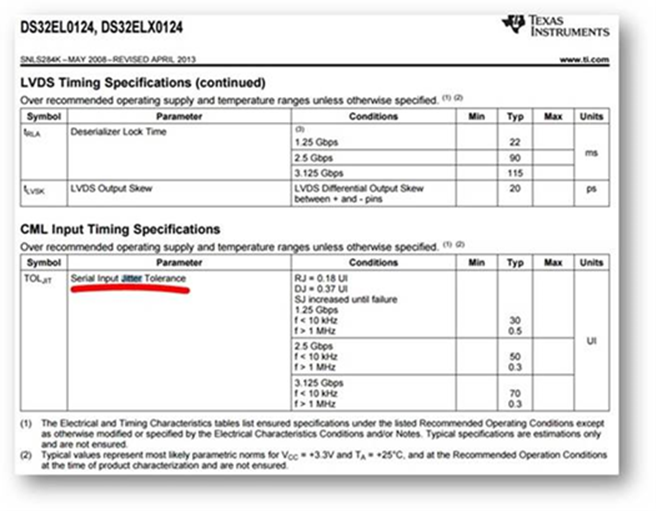

The way we read the “CML Input Timing Specification” for the “Serial Input Jitter Tolerance” parameter for a 3.125Gbps data rate is:

- The low frequency jitter (f<10KHz) is 70 UI. In other words, it is very tolerant of low frequency jitter. My customer says they've seen several UI before, but never 70 and want to verify that it is correct. Seeing as there is no errata or revision succeeding this stating otherwise, I assume it is. Just covering all my bases.

- The high frequency jitter (f>1MHz) is 0.3 UI or at 3.125Gbps which is (1/3.125Gbps)*(2)*0.3 = 192pSec (factor of 2 is conversion of bps to hertz). Correct?

- What is the jitter specification between 10KHz and 1MHz.

I appreciate any feedback you can offer on this subject.

-Amanda