Part Number: TLK10034

We are facing some difficulty while using the device TLK10034.

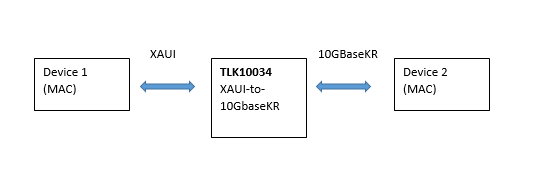

We are using the device in XAUI -to- 10G BaseKR mode as shown below.

(The DEVICE2 is on another board), other than the XAUI-10GBaseKr link, there is no connection between the DEVICE1 AND DEVICE2.

During testing we observed the following:

(1)After TLK10034 is brought out of reset, and the bit<15> of register 0x0001, set as '1', (expecting to power down the entire data path), the following is observed:

(i)Bit<2> of PCS_STATUS_1 (table 7-113) is 0

(ii)Bit<12> of KR_PCS_STATUS_1 (table 7-115) is 1, which indicates the 10GBaseKR link is up

After this the the bit<15> of register 0x0001, was set as '0"for normal operation, then the same registers were read as follows:

(i)Bit<2> of PCS_STATUS_1 (table 7-113) is 1

(ii)Bit<12> of KR_PCS_STATUS_1 (table 7-115) is 1

Now, when the data-path is again powered down by setting the the bit<15> of register 0x0001, as '1', there was no change in the PCS_Status bits , indicating that the links are up.The bits were read as:

(i)Bit<2> of PCS_STATUS_1 (table 7-113) is 1

(ii)Bit<12> of KR_PCS_STATUS_1 (table 7-115) is 1

The XSMI of TLK10034 is connected to Device1.There is no other interface connecting the device1 and device2.

Device1 knows the link status between TLK10034 and Device2 by reading the registers of TLK10034.Since these PCS status registers are not reliably indicating the status of the 10GBaseKR links, we are finding it difficult to know the status of Device2.

- Why is that the link status bits are not changing when bit<15> of register 0x0001 is set set as '1' for the second time?

Also, Why is the Bit<12> of KR_PCS_STATUS_1 not set to '0' when entire data path is powered down?