Part Number: HD3SS3220

Hi,

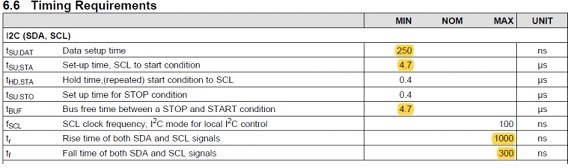

the maximum allowed I2C clock frequency is unclear to me.

Based on HD3SS3220 datasheet from "SLLSES1C –DECEMBER 2015–REVISED MAY 2017" section "6.6 Timing Requirements" table entry "fSCL" the SCL clock frequency is given as maximal "100 ns". Which means to me a minimum of 10Mhz is required, I know this is bullshit.

So what is the maximum SCL clock frequency. 100kHz, 400kHz or even better?