Other Parts Discussed in Thread: SN65DSI85

Hi All,

We are using an LVDS display in our product and we wanted to interface the LVDS display with qualcomm snapdragon 820 processor which support MIPI display. To convert MIPI to LVDS we have used SN65DSI85 in our design.

Our use case is transmitting Dual Split DSI output from processor i.e. half image of the complete display will be transferred to One DSI 4 lane port and other half display will be transferred to second DSI 4-lane port. We want the same scenario on the LVDS side that one display on LVDS1 will show the half portion of the complete image and second display will show the remaining half portion of the complete image.

I have attached the register settings with the case and below are our observations:

1.) We are able to receive the DSI data and clock lanes on the input side of SN65DSI85 both DSI ports.

2.) We are not able to receive the LVDS signals on both the LVDS ports. Only one port is working at a time. We want to see both the LVDS port working at the same time.

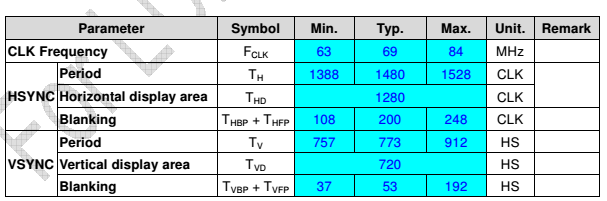

3.) The resolution of the display is 720P@60fps.

4.) The data on LVDS single port also sometimes doesn't work and sometimes it work.

Can somebody please verify the register setting and let us know the exact settings we need to use.