Part Number: SN65DSI85

Hi team,

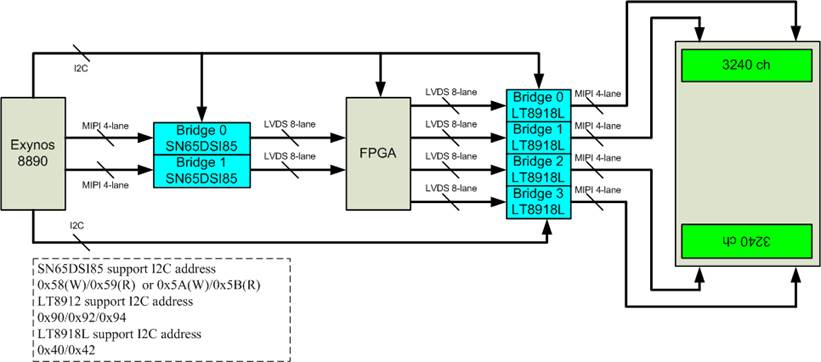

My customer BOE is evaluating SN65DSI85, they have two questions about this device as below. the attached is sch and reg setting, would you please kindly help? thanks.

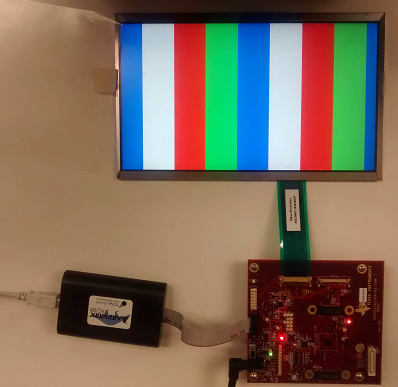

1. in test mode, what is the test pattern look like? they want to compare it with their test result

2. in normal mode, they would read 0x20 from CSR 0xE5, indicate uncorrectable ECC error. would you please suggest the possbile cause of ECC error? will power on sequence be a problem?

KevinDSI LVDS.zip