Hi,

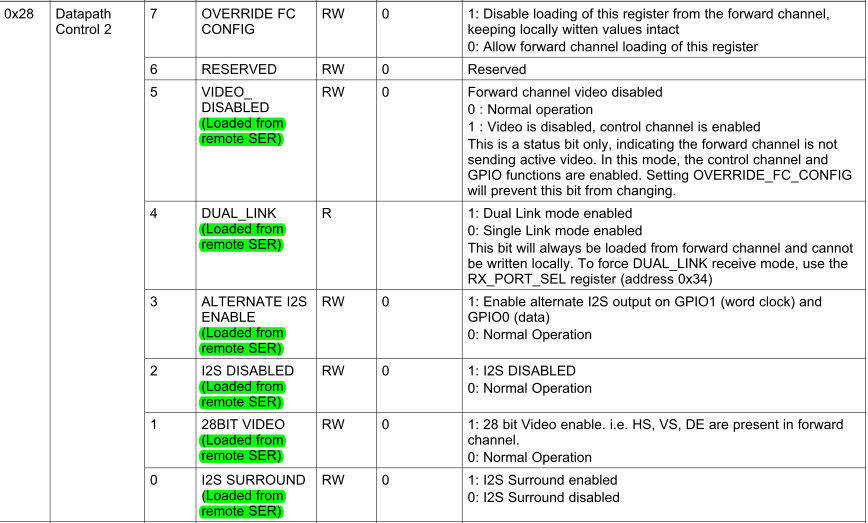

According to datasheet of DS90UH948, "Loaded from remote SER" is decribed in Add 0x28[5:0].

And I confirmed whether these bitfields are changed by using DS90UH949 when bitfield of "override fc config" is "0".

Then, I observed following result.

1. When I write 0x7F to DS90UH949, I observed 0x69 (I expected that 0x3F can be observed in Add 0x28 of DS90UH948).

2. When I write 0x7F to DS90UH949, I observed 0x20 (I expected that 0x00 can be observed in Add 0x28 of DS90UH948).

According to above result, following bitfields are not loaded from SER even though I set Add 0x28[7] of DS90UH948 to 0x0.

* 0x28[5] VIDEO_DISABLED

* 0x28[4] DUAL_LINK

* 0x28[2] I2S DISABLED

* 0x28[1] 28BIT VIDEO

So, Could you please send me correct information about which bitfield of Add 0x28 is loaded from SER when Add 0x28[7] is 0x0 ?

Best Regards,

Machida