Hi

We are urgently trying to set up a datapath scheme as per the attached ie 2x 953 going into 1x 964 , with 1x4 lane MIPI and 1x VC from each camera and 2x VCs going from the 946.

We are having issues setting this up - configuration attached.

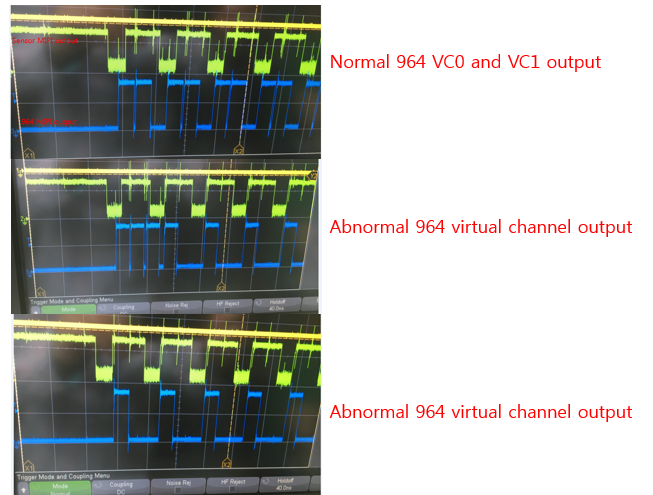

Both sensors can feed their 1x VC on the MIPI 4 lanes streams to 964 via each 953 and 964 can output MIPI 4 lanes to the "Processor" via VC0 and VC1.

But our team found that the 964 virtual channel output is sometimes abnormal on OVT side like below pictures attached. We assume that there is some configuration error but we are not sure what steps to take next to debug it.

Can you make a suggestion as to how we debug it - does the configuration attached look right?

many thanks

David

void API_SERDES_INIT_TI913_MIPI(u8 WhichDevice)

{

MID_SCCB_DEVICE_WRITE(WhichDevice,0x03, 0x48);// ;mode and coax

MID_SCCB_DEVICE_WRITE(WhichDevice,0x07, 0x28);// ;clock output, 25MHz to sensor. TI960 register 0x58 should set to 0x5E to set 953 FC to 4Gbps (3.2Gbps payload) to get this clock frequency

MID_SCCB_DEVICE_WRITE(WhichDevice,0x02, 0x73);// ;one lane MIPI, set to 73 if you need 4 lane MIPI

MID_SCCB_DEVICE_WRITE(WhichDevice,0x0e, 0xf0);// ;local GPIO

MID_SCCB_DEVICE_WRITE(WhichDevice,0x0D, 0x44);//

DELAY_MS(100);

MID_SCCB_DEVICE_WRITE(WhichDevice,0x0D, 0x46);//

DELAY_MS(100);

MID_SCCB_DEVICE_WRITE(WhichDevice,0x0D, 0x47);// //953 GPIO2->Frame synch, 953 GPIO1->SNR PWDNB, 953 GPIO0->SNR RESETB,

dprintf("rx0_953_setup_sync_mode_4g \n");

MID_SCCB_DEVICE_WRITE(TI964, 0x4C, 0x01);

debug_printf("964 RX0 0x00=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x00));

debug_printf("964 RX0 0x4d=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x4D));

debug_printf("964 RX0 0x5B=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x5B));

MID_SCCB_DEVICE_WRITE(TI964, 0x4C, 0x12);

debug_printf("964 RX1 0x00=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x00));

debug_printf("964 RX1 0x4d=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x4D));

debug_printf("964 RX1 0x5B=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x5B));

}

/**

Function: API_SERDES_INIT_TI964

Parameter: NONE

Return: NONE

*/

void API_SERDES_INIT_TI964(u8 snrID,u8 aliasID0,u8 aliasID1,u8 aliasID2,u8 aliasID3)

{

MID_SCCB_DEVICE_WRITE(TI964, 0x01, 0x02);//reset all digital part

DELAY_LOOP(5000);

MID_SCCB_DEVICE_WRITE(TI964, 0x0C, 0xCF); //I2C mappings.................

MID_SCCB_DEVICE_WRITE(TI964, 0x10, 0x91); //lock 0 to gpio 0, output frame synch

MID_SCCB_DEVICE_WRITE(TI964, 0x11, 0x85); //lock 1 to gpio 1

MID_SCCB_DEVICE_WRITE(TI964, 0x13, 0x89); //lock 3 to gpio 3

MID_SCCB_DEVICE_WRITE(TI964, 0x14, 0x8D); //lock 4 to gpio 4

MID_SCCB_DEVICE_WRITE(TI964, 0x19, 0x90); //FS_HIGH_TIME_1

MID_SCCB_DEVICE_WRITE(TI964, 0x1A, 0x00); //FS_HIGH_TIME_0

MID_SCCB_DEVICE_WRITE(TI964, 0x1B, 0xFF); //FS_LOW_TIME_1

MID_SCCB_DEVICE_WRITE(TI964, 0x1C, 0xFF); //FS_LOW_TIME_0

MID_SCCB_DEVICE_WRITE(TI964, 0x18, 0x01); //ENABLE FRAME SYNC

MID_SCCB_DEVICE_WRITE(TI964,0x0c, 0xcf);// ;enable port0-3 reveiver, map channel3 and channel2 to i2c port1, channel1/2 to i2c port0

MID_SCCB_DEVICE_WRITE(TI964,0x1f, 0x02);//;07 ; 100mhz reference clock, 400mbps serial rate (06, not access des)

MID_SCCB_DEVICE_WRITE(TI964,0x4c, 0x01);//; write enable for RX port 0

MID_SCCB_DEVICE_WRITE(TI964,0x58, 0x5e);//;50Mbps back channel

MID_SCCB_DEVICE_WRITE(TI964,0x5c, 0x34);// ;serializer alias ID

MID_SCCB_DEVICE_WRITE(TI964,0x5d, 0x6c);// ;sensor 7251 ID

MID_SCCB_DEVICE_WRITE(TI964,0x65, aliasID0);// ;sensor alias ID

MID_SCCB_DEVICE_WRITE(TI964,0x6d, 0x7c);// ;CSI configure, FPD input mode, enable coax cable

MID_SCCB_DEVICE_WRITE(TI964,0x7c, 0x01);// ; frame polarity

MID_SCCB_DEVICE_WRITE(TI964,0x70, 0x2b);// ; port 0 raw 10 data type

MID_SCCB_DEVICE_WRITE(TI964,0x71, 0x2c);// ; raw 12 data type

MID_SCCB_DEVICE_WRITE(TI964,0x72, 0x00);// ; virtual channel 0 00 for DCG16 04 for DCG12+VS12

MID_SCCB_DEVICE_WRITE(TI964,0x6F, 0x0A);// BCC GPIO2 select frame sync signal

MID_SCCB_DEVICE_WRITE(TI964,0x4c, 0x12);//; write enable for RX port 1

MID_SCCB_DEVICE_WRITE(TI964,0x58, 0x5e);//

MID_SCCB_DEVICE_WRITE(TI964,0x5c, 0x38);//

MID_SCCB_DEVICE_WRITE(TI964,0x5d, 0x6c);//

MID_SCCB_DEVICE_WRITE(TI964,0x65, aliasID1);// ; senslor alias id

MID_SCCB_DEVICE_WRITE(TI964,0x6d, 0x7c);//

MID_SCCB_DEVICE_WRITE(TI964,0x7c, 0x01);//

MID_SCCB_DEVICE_WRITE(TI964,0x70, 0x6b);// ; port1 raw 10 data type

MID_SCCB_DEVICE_WRITE(TI964,0x71, 0x6c);// ; port 1 raw 12

MID_SCCB_DEVICE_WRITE(TI964,0x72, 0x01);// ; virtual channel 1

MID_SCCB_DEVICE_WRITE(TI964,0x6F, 0x0A);// BCC GPIO2 select frame sync signal

/*

MID_SCCB_DEVICE_WRITE(TI964,0x4c, 0x24);// ; write enable for RX port 2

MID_SCCB_DEVICE_WRITE(TI964,0x58, 0x5e);//

MID_SCCB_DEVICE_WRITE(TI964,0x5c, 0x38);//

MID_SCCB_DEVICE_WRITE(TI964,0x5d, 0x6c);//

MID_SCCB_DEVICE_WRITE(TI964,0x65, aliasID2);// ;senslor alias id

MID_SCCB_DEVICE_WRITE(TI964,0x6d, 0x7c);//

MID_SCCB_DEVICE_WRITE(TI964,0x7c, 0x01);//

MID_SCCB_DEVICE_WRITE(TI964,0x70, 0x2b);//

MID_SCCB_DEVICE_WRITE(TI964,0x71, 0x2c);//

MID_SCCB_DEVICE_WRITE(TI964,0x72, 0x00);//

MID_SCCB_DEVICE_WRITE(TI964,0x4c, 0x38);//; write enable for RX port 3

MID_SCCB_DEVICE_WRITE(TI964,0x58, 0x5e);//

MID_SCCB_DEVICE_WRITE(TI964,0x5c, 0xb0);//

MID_SCCB_DEVICE_WRITE(TI964,0x5d, 0x6c);//

MID_SCCB_DEVICE_WRITE(TI964,0x65, aliasID3);//

MID_SCCB_DEVICE_WRITE(TI964,0x6d, 0x7c);//

MID_SCCB_DEVICE_WRITE(TI964,0x7c, 0x01);//

MID_SCCB_DEVICE_WRITE(TI964,0x70, 0x2b);//

MID_SCCB_DEVICE_WRITE(TI964,0x71, 0x2c);//

MID_SCCB_DEVICE_WRITE(TI964,0x72, 0x01);//

*/

//MID_SCCB_DEVICE_WRITE(TI964,0xb0, 0x14);//;04

//MID_SCCB_DEVICE_WRITE(TI964,0xb1, 0x03);//

//MID_SCCB_DEVICE_WRITE(TI964,0xb2, 0x04);//

//MID_SCCB_DEVICE_WRITE(TI964,0xb1, 0x04);//

//MID_SCCB_DEVICE_WRITE(TI964,0xb2, 0x04);//

MID_SCCB_DEVICE_WRITE(TI964,0x4c, 0x01);//

MID_SCCB_DEVICE_WRITE(TI964,0x32, 0x01);// ; enable write for TX Port0

MID_SCCB_DEVICE_WRITE(TI964,0x33, 0x03);// ; enable CSI output

MID_SCCB_DEVICE_WRITE(TI964,0x32, 0x12);// ; enable write for TX Port1

MID_SCCB_DEVICE_WRITE(TI964,0x33, 0x03);// ; Enable CSI output

MID_SCCB_DEVICE_WRITE(TI964,0x20, 0x0c);// ; mp virtual channel to CSI port 1

MID_SCCB_DEVICE_WRITE(TI964,0x21, 0x03);// ; configure CSI output port1/0

MID_SCCB_DEVICE_WRITE(TI964,0xd5, 0xc0);// very import for 953 detect

MID_SCCB_DEVICE_WRITE(TI964,0x4c, 0x12);//

MID_SCCB_DEVICE_WRITE(TI964,0x32, 0x01);// ; enable write for TX Port0

MID_SCCB_DEVICE_WRITE(TI964,0x33, 0x03);// ; enable CSI output

MID_SCCB_DEVICE_WRITE(TI964,0x32, 0x12);// ; enable write for TX Port1

MID_SCCB_DEVICE_WRITE(TI964,0x33, 0x03);// ; Enable CSI output

MID_SCCB_DEVICE_WRITE(TI964,0x20, 0x0c);// ; mp virtual channel to CSI port 1

MID_SCCB_DEVICE_WRITE(TI964,0x21, 0x03);// ; configure CSI output port1/0

MID_SCCB_DEVICE_WRITE(TI964,0xd5, 0xc0);// very import for 953 detect

// MID_SCCB_DEVICE_WRITE(TI964,0xb8, 0x18);//

dprintf("ti964_enable done\n");

// MID_SCCB_DEVICE_WRITE(TI964, 0x4C, 0x01);

// MID_SCCB_DEVICE_WRITE(TI964, 0x5C, MID_SCCB_DEVICE_READ(TI964, 0x5B));//ser id=0xb0, auto load from remote ser even without 964 init

}

#if 1

API_SERDES_INIT_TI964(0x6c,0x64,0x62,0x68,0x6a);

DELAY_MS(250);

API_SERDES_INIT_TI913_MIPI(TI913_0);

MID_SCCB_DEVICE_WRITE(TI964, 0x4C, 0x01);

debug_printf("964 RX0 0x00=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x00));

debug_printf("964 RX0 0x4d=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x4D));

debug_printf("964 RX0 0x5B=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x5B));

API_SERDES_INIT_TI913_MIPI(TI913_1);

MID_SCCB_DEVICE_WRITE(TI964, 0x4C, 0x12);

debug_printf("964 RX1 0x00=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x00));

debug_printf("964 RX1 0x4d=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x4D));

debug_printf("964 RX1 0x5B=%x\r\n",MID_SCCB_DEVICE_READ(TI964, 0x5B));

dprintf("check snr0 ID\n");

MID_SENSOR_DETECT(MIPI_PATH_0);

dprintf("check snr1 ID\n");

MID_SENSOR_DETECT(MIPI_PATH_1);

dprintf("load snr0 setting\n");

API_SetSubSetting(3);

dprintf("load snr1 setting\n");

API_SetSubSetting(4);

dprintf("check snr0 ID again\n");

MID_SENSOR_DETECT(MIPI_PATH_0);

dprintf("check snr1 ID again\n");

MID_SENSOR_DETECT(MIPI_PATH_1);

dprintf("load dp setting\n");

API_SetSubSetting(0);//dp

dprintf("stream on sensor0\n");

MID_SCCB_DEVICE_WRITE(MIPI_PATH_0, 0x3012, 0x01);//stream on

dprintf("stream on sensor1\n");

MID_SCCB_DEVICE_WRITE(MIPI_PATH_1, 0x3012, 0x01);//stream on

dprintf("check snr0 ID again\n");

MID_SENSOR_DETECT(MIPI_PATH_0);

dprintf("check snr1 ID again\n");

MID_SENSOR_DETECT(MIPI_PATH_1);

#endif