Part Number: SN75LVDS83B

Other Parts Discussed in Thread: TFP401,

Hello,

We are taking an HDMI input into a TFP401 / SN75LVDS83B combination to drive a 10.1" LVDS display. We have our first prototype board and the circuit seems to be functioning correctly but the display is unable to recognize any input source. Specifically, the display stays in a sort of test mode and cycles through entire RGB screens every couple of seconds or so. I've tested the display driven by a OEM LVDS driver without problem. The PCB follows the differential impedance calculations and the various guidelines for high speed LVDS signals.

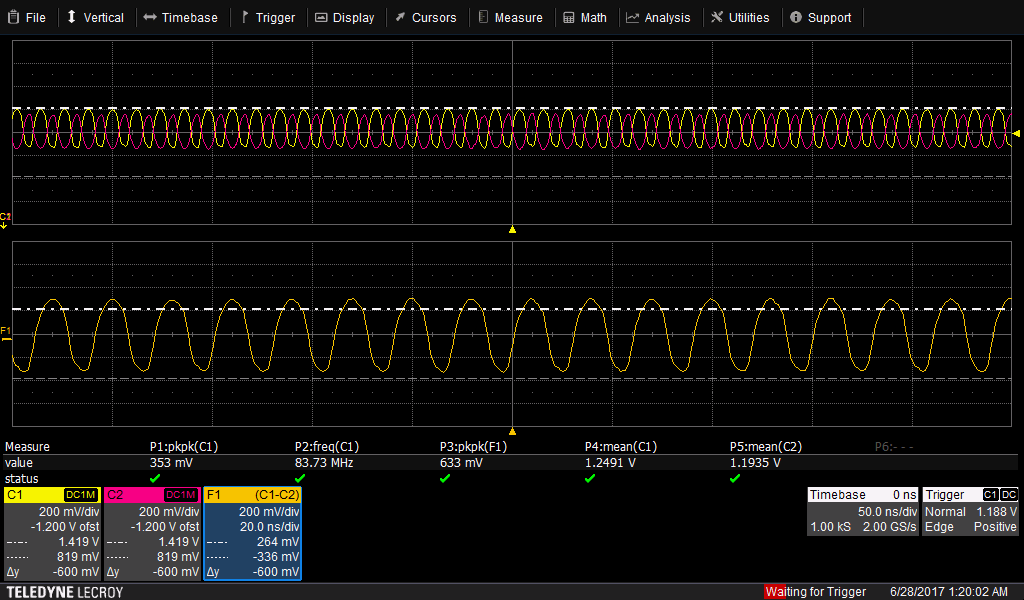

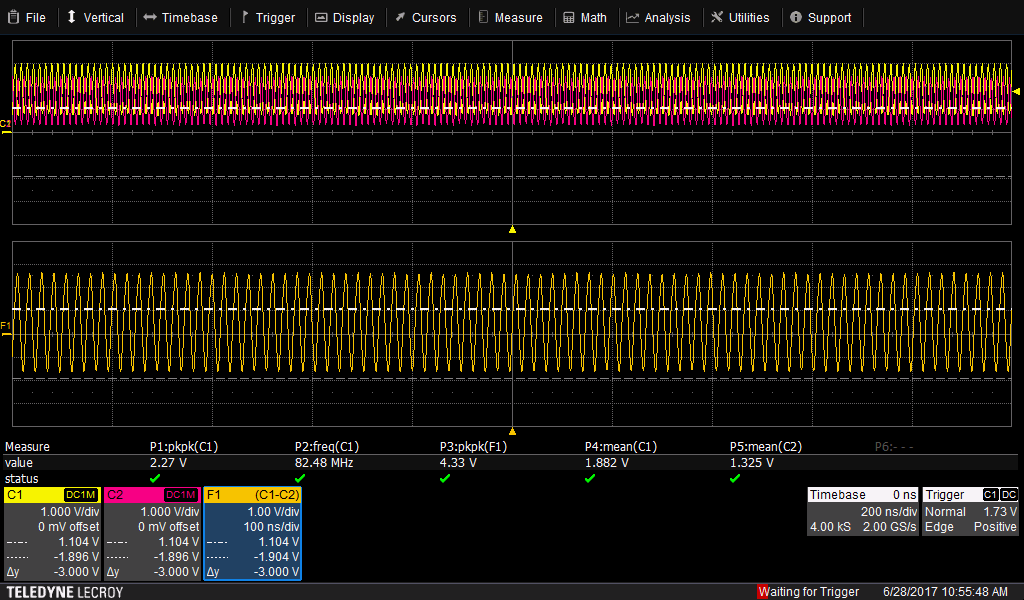

When comparing the signals from the OEM board and our prototype the voltage levels look to be quite a bit different. Here is a capture of the clock signal from our prototype measured from the receiver side with two single ended probes. We do not have access to a differential probe with enough bandwidth to measure this. F1 is the math difference. The LVDS voltage levels look sufficient with a swing of about 350mV on each line and 630mV via the difference. The OEM board on the other hand drives their signals at a swing of over 2V. What am I missing here? Based on the SN75LVDS83B output specs, it is outputting correctly and the LVDS input should be acceptable for the display. Yet I'm still not getting any output on the display. Thoughts?

Prototype LVDS Clock

OEM Driver Clock Signal

- Mark