Hi,

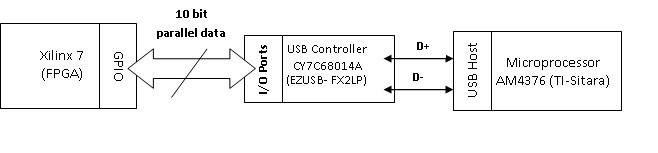

I have interfaced Xilinx 7 Series FPGA with TI processor- Sitara AM4376 over USB2.0.

I have implemented USB PHY through Cypress USB Controller IC - CY7C68014A (EZUSB-FX2LP). The attached file is the architecture I have implement for USB PHY between processor and FPGA. I can establish the data transfer from processor to FPGA from D+/D- to parallel data.

I am confused with how shall I send the data from FPGA to processor back, over USB when a respective request command is received by FPGA from processor. I have used processor in USB host mode and FPGA as a slave device mode.

Can some one help with this.