Other Parts Discussed in Thread: DS92LV0422

Dear Sir/Madam,

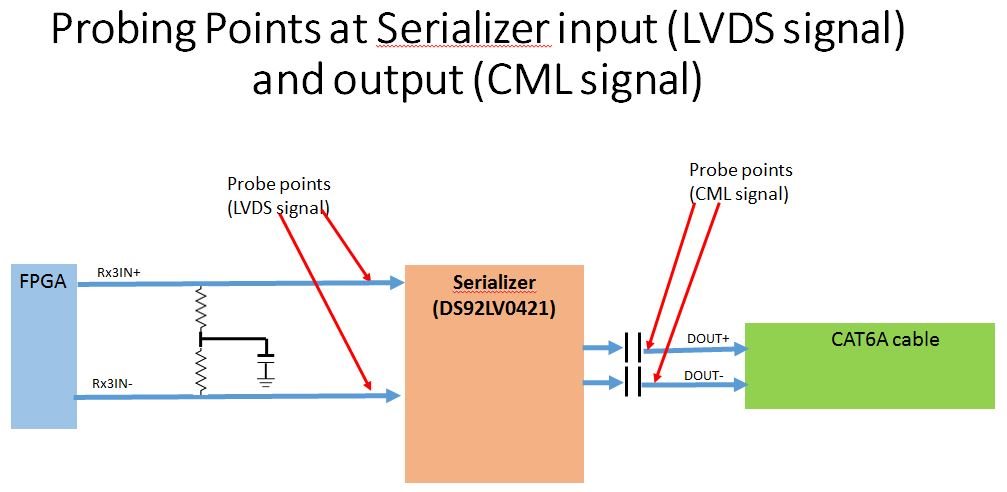

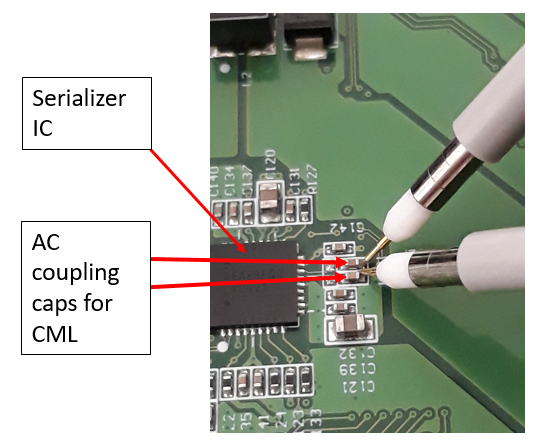

I am using DS92LV0421 as serializer from LVDS input signal to CML output signal. Below is my setup for my measurement:

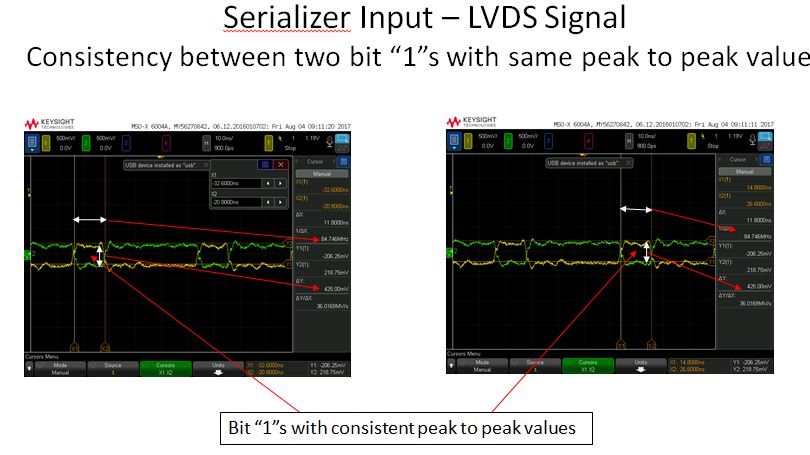

Here is my input waveform, look ok!

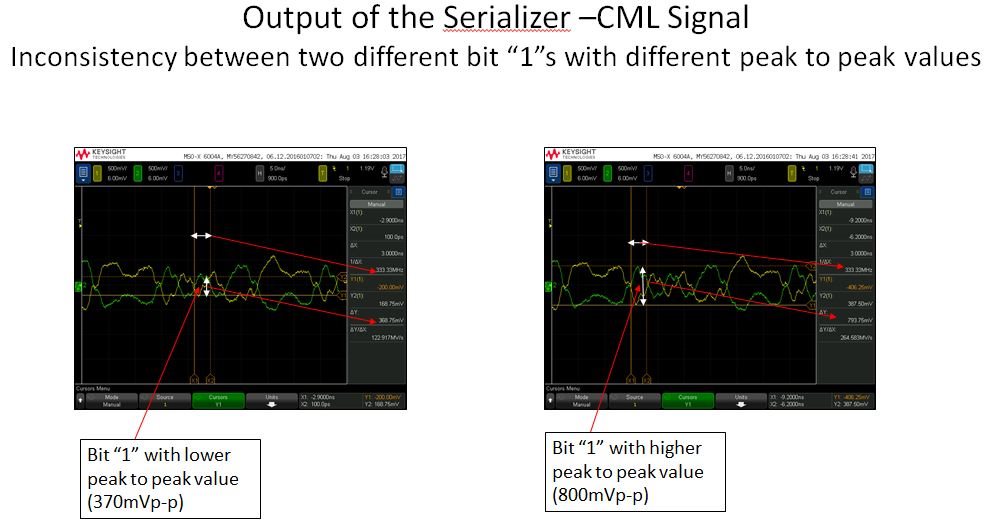

But my output waveform look a bit strange.

With respect to the above mentioned observation we would be grateful if you could help to clarify the below mentioned doubts.

- Is our probing points and methods are correct ?

- Why the CML signal at the Serializer output gives different peak to peak values for different bit “1”s ?

- If different peak to peak values are acceptable, how to quantify it ?

- If different peak to peak values are not acceptable, what is the method to correct it in terms of either hardware or software ?

- Do you have any advice how can I improve my CML output?

Just some of the info with respect to our system that could be useful to you.

- Clock frequency = 12 MHz

- Bit rate per LVDS channel = 12x7 = 84Mbps

- Bit rate at the CML output = 12x7x4 = 336Mbps

Best regards,

kpk