Other Parts Discussed in Thread: SN75LVDS83B, , TFP401

Hi,

we need to convert HDMI to drive a LVDS panel (see attached datasheets of both display and controller

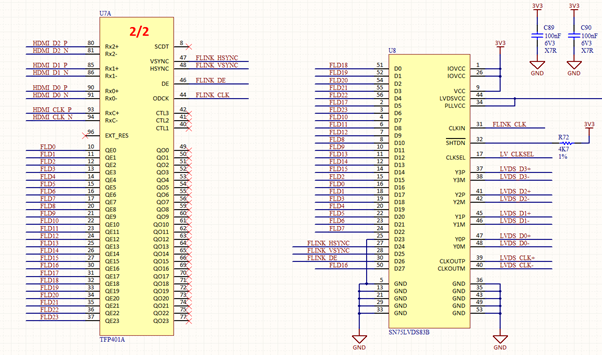

We are using the TFP401A together with the SN75LVDS83B. Please see the schematic below to see how we connected the two ICs.

Questions:

1) About connectivity between the two TI chips. According to the attached TI app notes and datasheets there are a number of different ways to connect the two TI chips to each other. It looks like that depends on the display driving pattern. But we could not make much sense. In our schematic you can see how we connected them together but we don’t think the way we connected them is correct because the data from a supplier shows a different configuration (but we only have partial information on that). So could you please show/let me know the correct connectivity to drive the attached display in both 6 bit and also in 8 bit configuration of the display.

2) Following from the above question, could you please explain more clearly the logic behind the connection between the two TI chips? Could you please explain it in detail.

3) Also in terms of routing between the SN75LVDS83B and the TFP401, do the traces need to be routed with a controlled impedance?

4) if so, what is the maximum mismatch in trace length between all traces between the two chips?

Many thanks

Rick