Hi Moises-san,

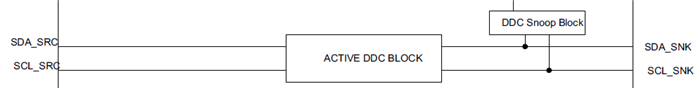

Our customer use TMDS181 in sink side application(Figure.36) and would like to know about active DDC block.

Referring the Functional Block Diagram on the TMDS181 datasheet, DDC lines includes active DDC block.

Does it mean that the capacitive load on SCL_SRC and SCL_SNK as well as SDA_SRC and SDA_SNK are electrically isolated?

Another words, is the capacitance connected on SNK side not seen from SRC side vice versa?

If no (so those pins aren’t isolated), could you please let us know about max value of parasitic capacitance of SCL_SRC and SDA_SRC pins

(if you don’t have the max value, we need a histogram of the Parasitic capacitance.)

I’d greatly appreciate your verification.

Regards,

Kanemaru