Part Number: TMDS181

Hi dear supporting team,

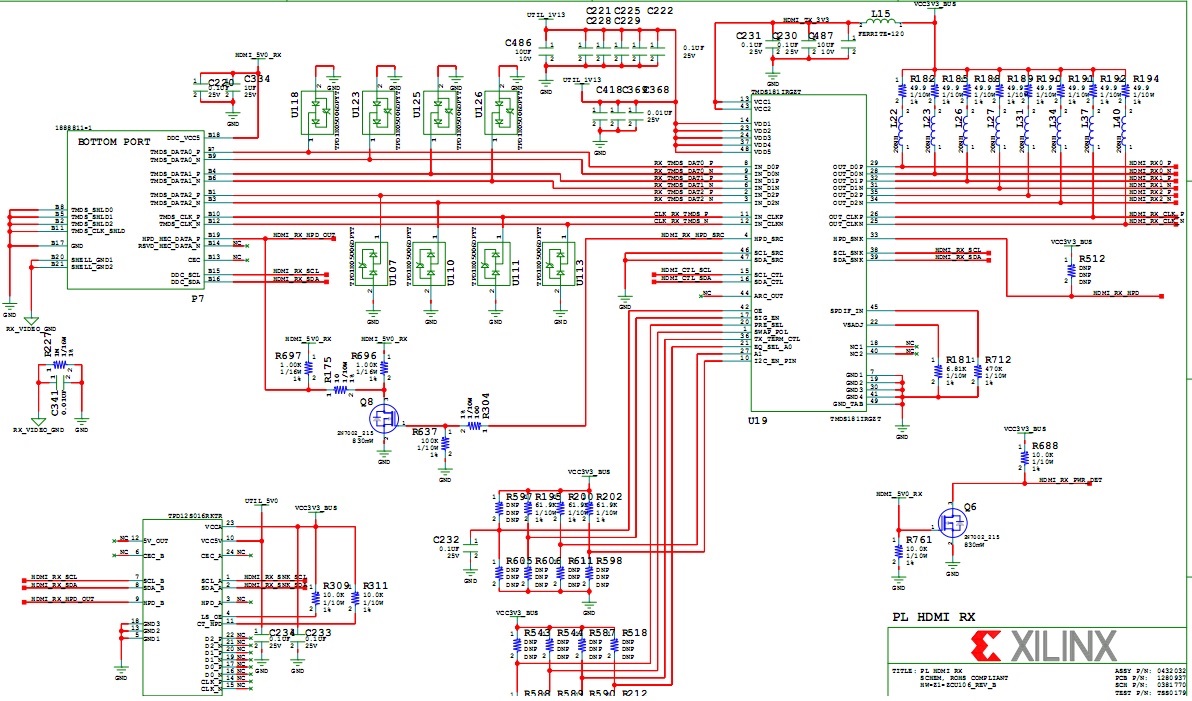

my customer is evaluating XILINX evk with TMDS181 on it, the setup is camera input to TMDS181, and then to FPGA. the sch is as attached.

while they found there is no output even there is singal input to our chip. and they are running at HDMI2.0, TMDS181 powering up with default setting.

pls help comment which regs need be changed. tks!

regisiter address offset(hex) | value(hex)

0x0 0x54

0x1 0x4D

0x2 0x44

0x3 0x53

0x4 0x31

0x5 0x38

0x6 0x31

0x7 0x20

0x8 0x1

0x9 0x2

0xA 0xB1

0xB 0x0

0xC 0x0

0xD 0x0

0xE 0x0

0xF 0xF

0x10 0x0

0x11 0x0

0x12 0x0

0x13 0x0

0x14 0x0

0x15 0x0

0x16 0x0

0x17 0xF0

0x18 0x0

0x19 0x0

0x1A 0x0

0x1B 0x0

0x1C 0x0

0x1D 0x0

0x1E 0x0

0x1F 0x0

0x20 0x4A