Other Parts Discussed in Thread: TLK10232

Hi Team,

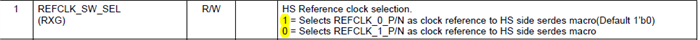

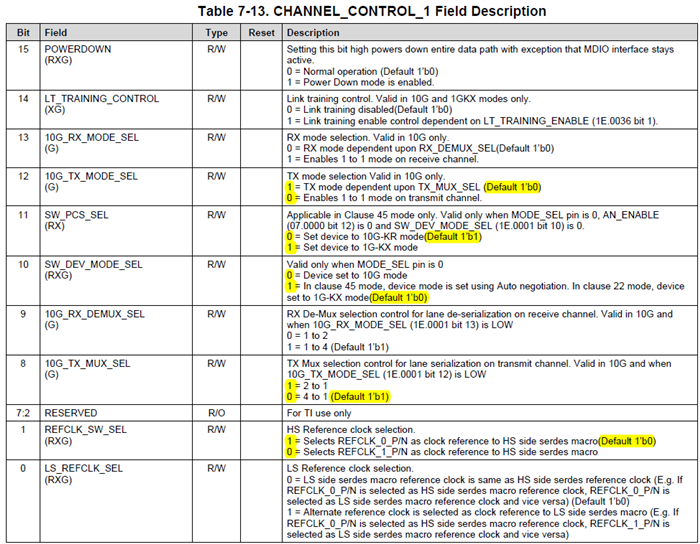

We would like to know the default value of bit1 of CHANNEL_CONTROL_1.

I am confused in the contents of the data sheet…

I understand that the position of "0" and "1" is a mistake.

If yes, we believe that this default value is “0”(so Selects REFCLK_0_P/N) because “Default 1’b0” is mentioned in datasheet.

Is my understanding correct?

Regards,

Kanemaru