Part Number: TUSB1002

Hello.

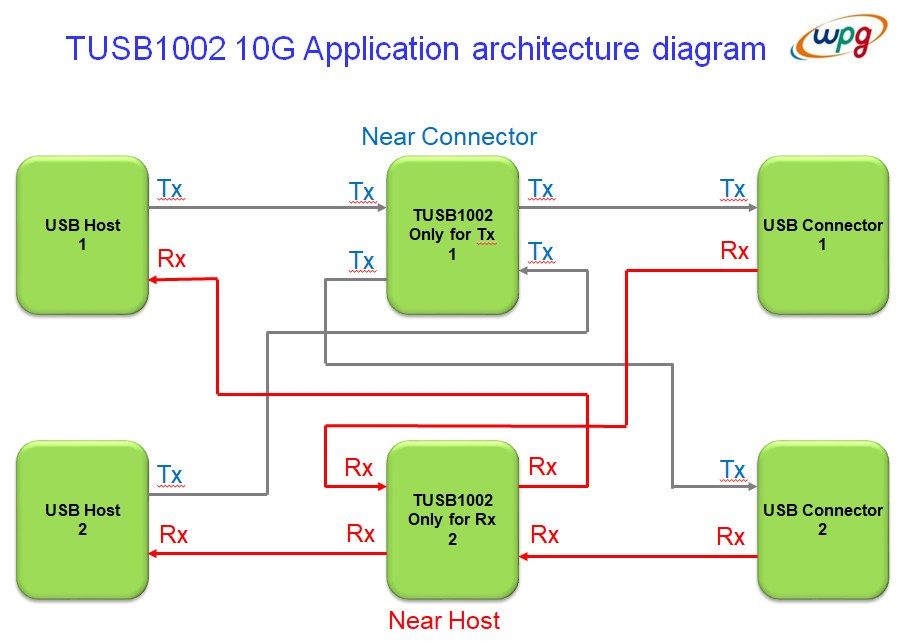

We have a project used two TUSB1002 for two USB ports. One TUSB1002 only for TX and other one TUSB1002 is only to RX. Like below diagram. We have some question need you help on below. Thanks~

1. Have any customer use below architecture diagram for project?

2. USB Rx/Tx whether the differential signal needs the same length?

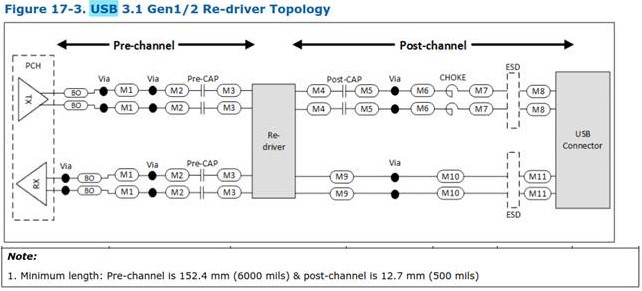

3. USB Pre-channel can we less than 6 inch? maybe like 3.5 inch. and Post-channel length can we greater than 0.5 inch? we will less than 2 inch in length. Please reference Figure 17-3 from Intel PDG.

4. In this architecture diagram can we pass USB test? like LFPS. When I set SLP_S0# to 0.

5. In this architecture diagram how should I set the MODE and SLP_S0 # pins?

6. TUSB1002 Pin14 SLP_S0# function is Receiver Detect Control or sleep mode control?