Part Number: SN65DSI84

Dear TI,

Please help us with DSI tuner values for dual lvds mode settings with frame rate of 60Hz.

Because when we are setting it to 60fps display works fine at first time but after reboot

display is not at all working, need your help in finding out proper values to input in DSI tuner tool.

We are using display of Module 15.6”FHD Color TFT-LCD, Model Name "G156HTN02.0" .

Please find snapshots of values used on DSI tuner tool.

LCD SPEC

timing5: timing5 {

screen-type = <SCREEN_MIPI>;

lvds-format = <LVDS_8BIT_1>;

out-face = <OUT_P888>;

clock-frequency = <141860000>;

hactive = <1920>;

vactive = <1080>;

hback-porch = <30>;

hfront-porch = <60>;

vback-porch = <10>;

vfront-porch = <15>;

hsync-len = <15>;

vsync-len = <5>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

swap-rb = <0>;

swap-rg = <0>;

swap-gb = <0>;

swap-delta = <0>;

swap-dummy = <0>;

};

void DSI84_MIPI_to_DUAL_LVDS_G156HTN020()

{

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_SOFT_RESET , 0x00);// reg 0x09

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CORE_PLL , 0x05);// reg 0x0a

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_PLL_DIV , 0x28);// reg 0x0b

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_PLL_EN , 0x00);// reg 0x0d

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_DSI_CFG , 0x26);// reg 0x10

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_DSI_EQ , 0x00);// reg 0x11

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_DSI_CLK_RNG , 0x55);// reg 0x12

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_LVDS_MODE , 0x6c);// reg 0x18

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_LVDS_SIGN , 0x00);// reg 0x19

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_LVDS_TERM , 0x03);// reg 0x1a

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_LVDS_CM , 0x00);// reg 0x1b

//W=1920

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_LINE_LEN_LO , 0x80);// reg 0x20

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_LINE_LEN_HI , 0x07);// reg 0x21

//H=1080

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_VERT_LINES_LO , 0x38);// reg 0x24

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_VERT_LINES_HI , 0x04);// reg 0x25

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_SYNC_DELAY_LO , 0x20);// reg 0x28

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_SYNC_DELAY_HI , 0x00);// reg 0x29

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_HSYNC_WIDTH_LO , 15);// reg 0x2c

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_HSYNC_WIDTH_HI , 0);// reg 0x2d

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_HORZ_BACKPORCH , 30);// reg 0x34

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_HORZ_FRONTPORCH , 60);// reg 0x38

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_VSYNC_WIDTH_LO , 5);// reg 0x30

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_VSYNC_WIDTH_HI , 0);// reg 0x31

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_VERT_BACKPORCH , 10);// reg 0x36

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_VERT_FRONTPORCH , 15);// reg 0x3a

i2c_reg_write(SN65DSI84_I2C_ADDR, DSI84_CHA_TEST_PATTERN , 0x00);// reg 0x3c

}

rockchip,dsi_hs_clk = <851.16>;

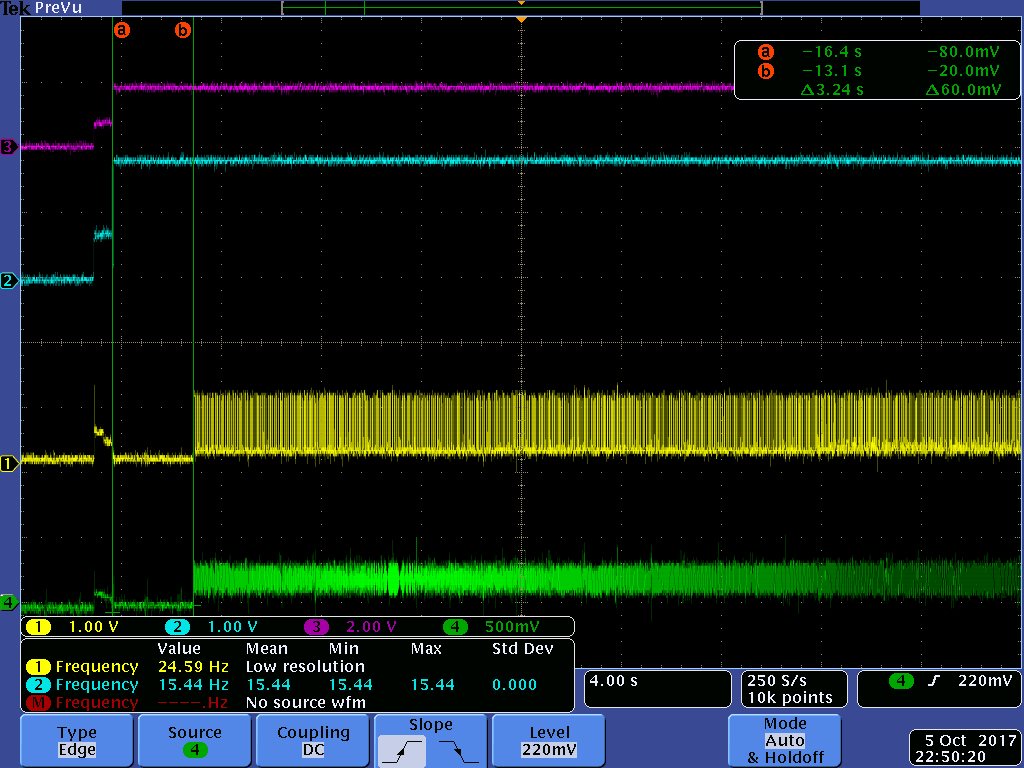

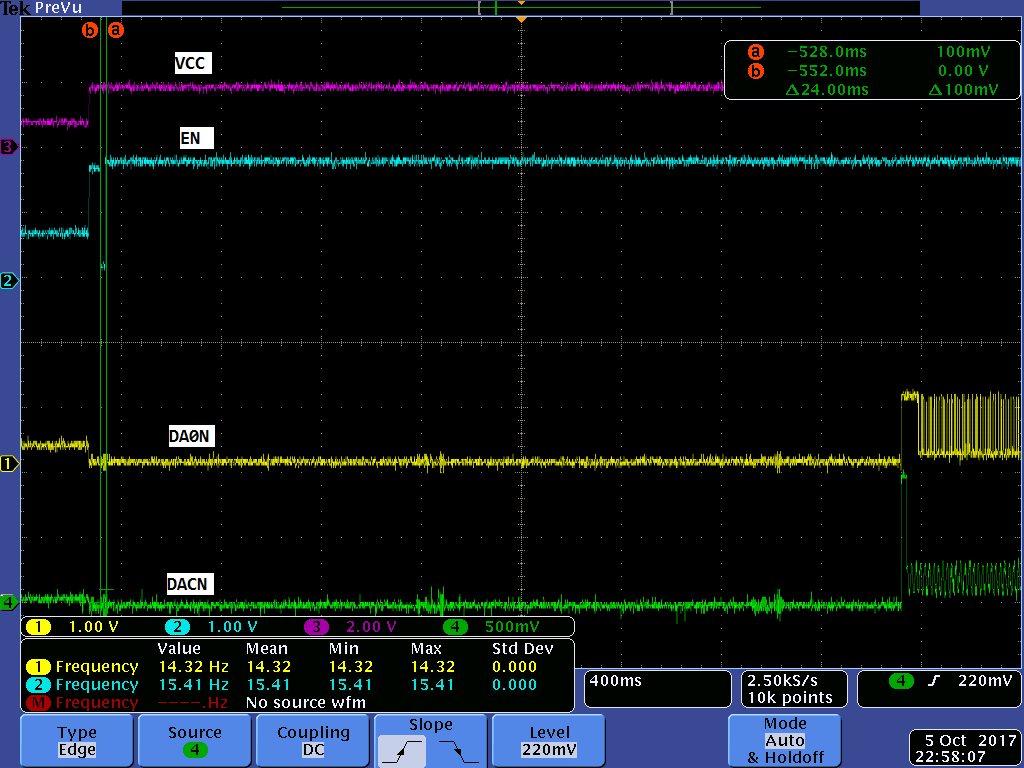

use debug board . and use command " dumpsys display | grep DisplayModeRecord "

can see fps : DisplayModeRecord{mMode={id=1, width=1920, height=1080, fps=63.000004}}