Other Parts Discussed in Thread: TFP401A, TFP401

Hi all

Would you mind if we ask TFP401A-Q1?

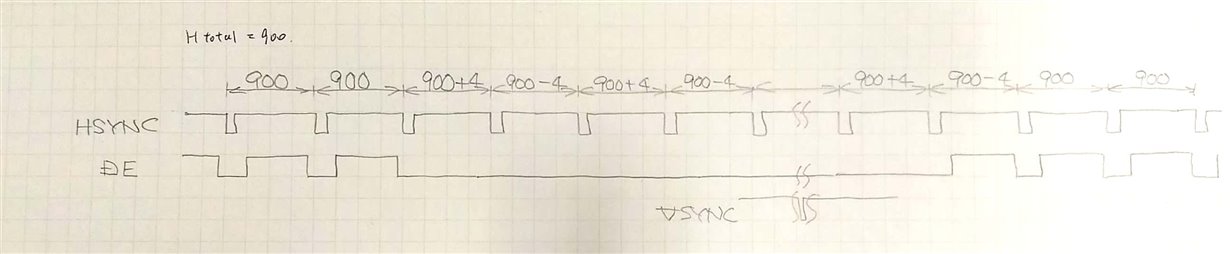

Could you refer to the attachment file?

In case of except for horizontal period of the input signal which is 8 multiples of CLK value, it occurs jitter at Hsync during blanking time.

For example, Htotal + 4clk -> Htotal - 4clk -> Htotal + 4clk,,,

<Question>

Is it normal opretation?

If it is not normal operation, could you let us know the method for it?

And then, if the information we served is not enough, could you let us know?

Kind regards,

Hirotaka Matsumoto