Part Number: DP83867IS

Tool/software: Linux

Hi,

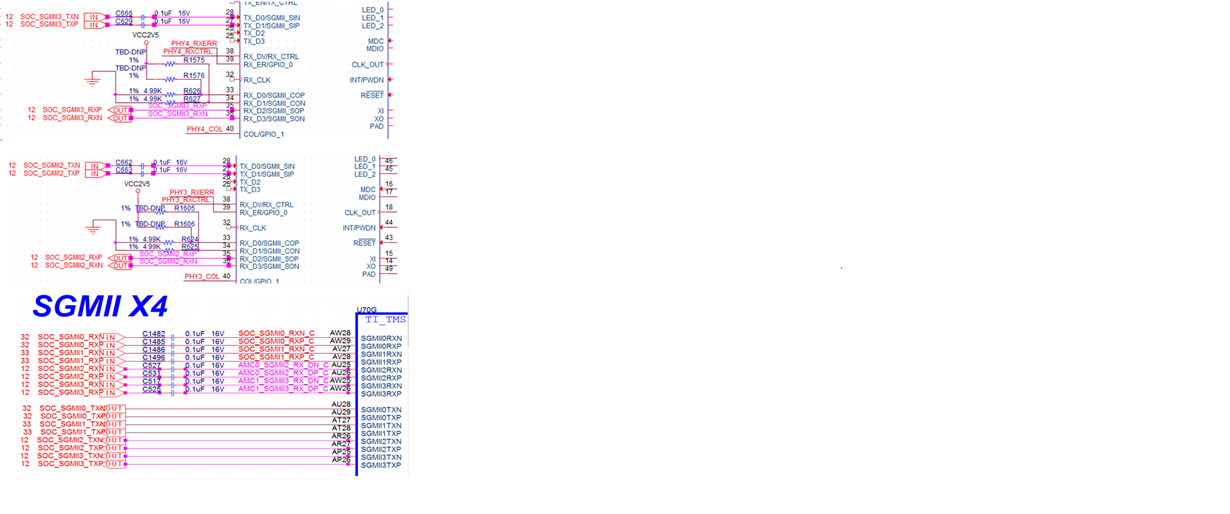

We are trying to bring up the four 1Gig Ethernet ports in customized k2hk board.

-> First two Ethernet ports ( eth0 and eth1) with Marvell chip using sgmii interface.

status: working, as in the k2hk evm board

-> other two Ethernet ports (eth2 and eth3 ) with TI DP83867 using sgmii interface.

status: Shows up the interface, but unable to ping.

step followed to bring up TI DP83867

In kernel

-> because of unavailability of driver for dp83867 in mcsdk kernel , we moved from mcsdk to Processor SDK .

-> we did the changes in device tree , PFA of device tree.

-> we did the changes in dp83867 driver, because it support only RGMII mode, but we need SGMII mode of operation, PFA of modified driver and original driver .

-> SGMII mode related modification are borrowed from the boot loader file ti.c , PFA of ti.c

We also tried in PSDK Boot loader

-> Enabled the ti.c which in in the path /driver/net/phy/ti.c , tried to ping other ip , but system restarts.

Please help us in getting this up.

Thanks,

Gireesh Hiremath

Senior design engineer

Lekha Wireless Solution

Bangalore