Part Number: SN65DSI83EVM

Other Parts Discussed in Thread: SN65DSI83

Tool/software: Linux

Hi Guys:

I had used sn65dsi83 on my project, the soc is qualcomm MSM8909, and the display almost ok, but I still have a question here:

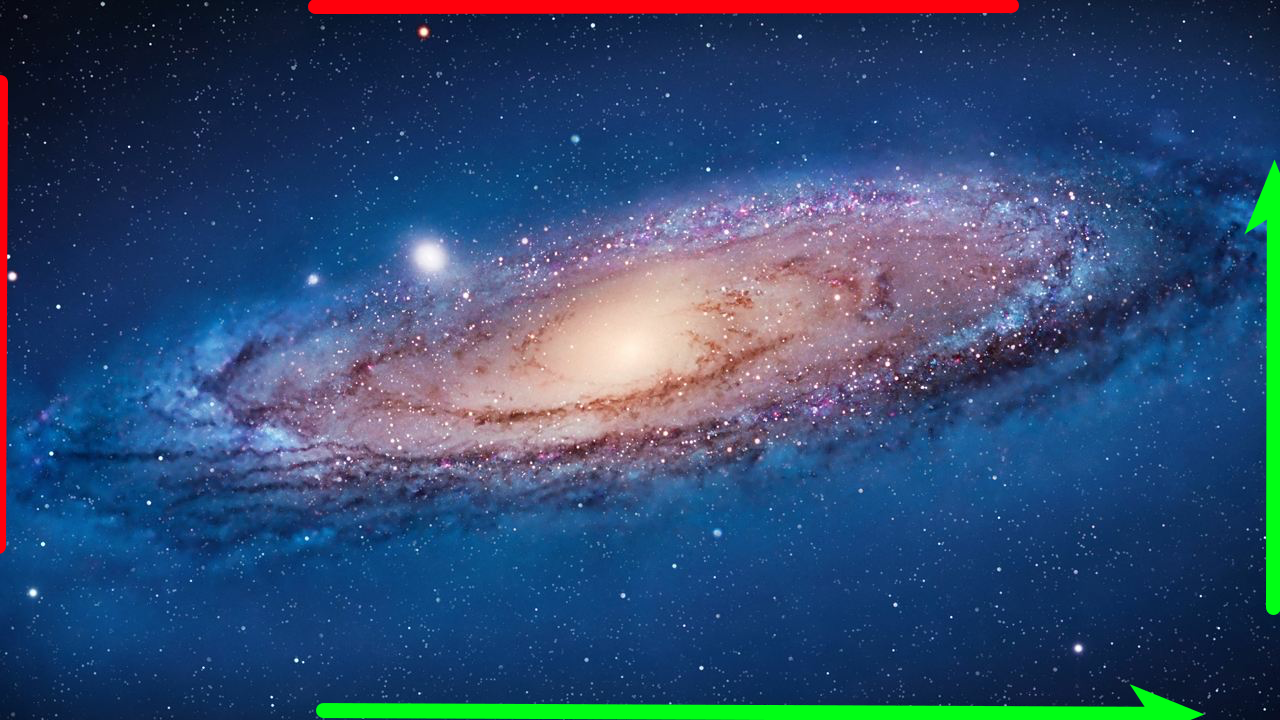

my original picture is :

but the display show:

The button of the display works abnormal, did you have any suggestion for me?

Thanks.

B.R.