Part Number: DS90C387

Other Parts Discussed in Thread: DS90CF388

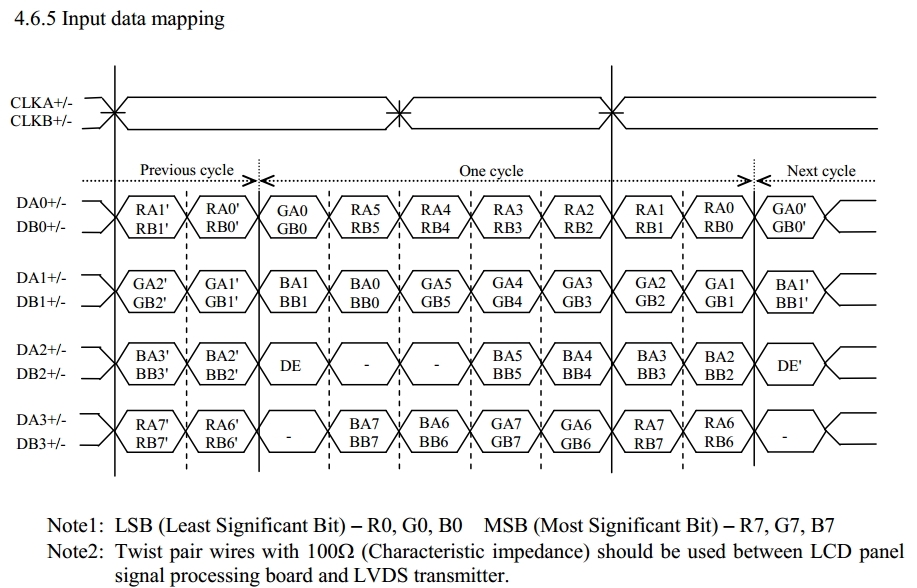

Hi, we are looking at using AM5728 work with DS90C387 to display on one Full HD LCD(1920*1080). Since the pixel counts is huge, The LCD requires 2 port LVDS for odd pixel and even pixel transmission in same time. The data mapping requirment is showed in attach.

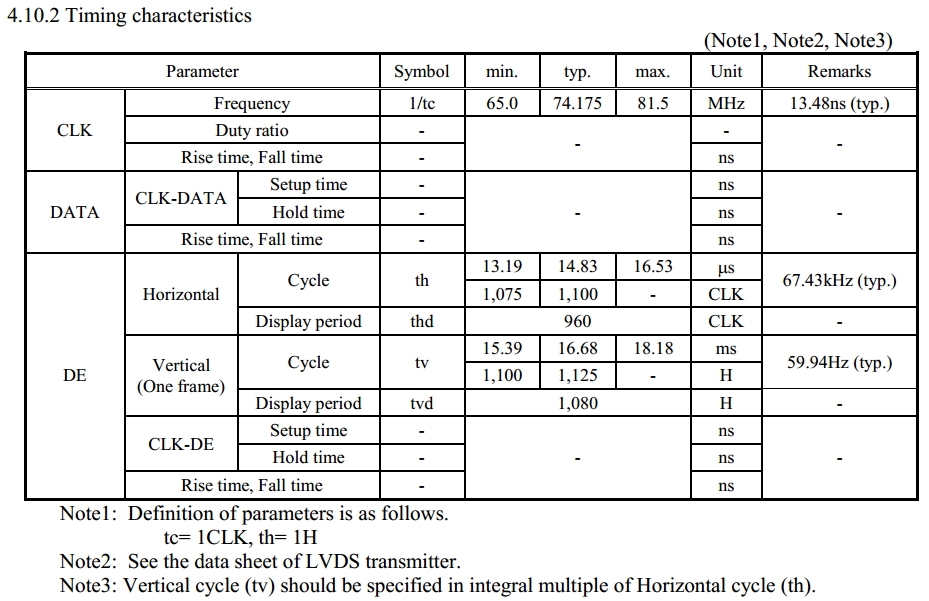

We are wondering if DS90C387 is configured in SINGLE TO DUAL PIXEL mode,AM5728 use one LCD buffer, like LCD1 to output 24 bit RGB continously in which containing odd and even pixel data, then DS90C387 split them to 2 LVDS port, one for odd pixel, another for even pixel? Does that workable? If yes, what's the pixel clock(output from AM5728) relationship with LVDS clk(output from DS90C387 )?

How is DS90C387 able to recognize odd and even pixel data when it is splitting?

Thanks.