Part Number: PCA9548A

Hi,

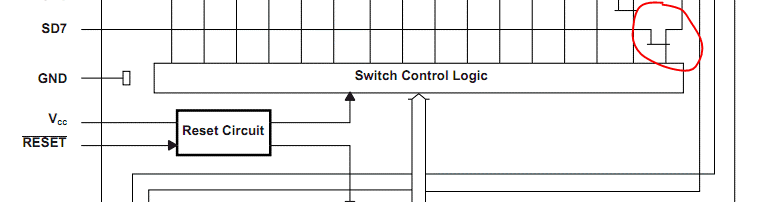

Can anyone tell me if PCA9548A is under reset, what status will SCL,SDA,SC0-7,SD0-7 pins be? Could these pins be tied with GND? All these pins are pulled up to 3.3V.

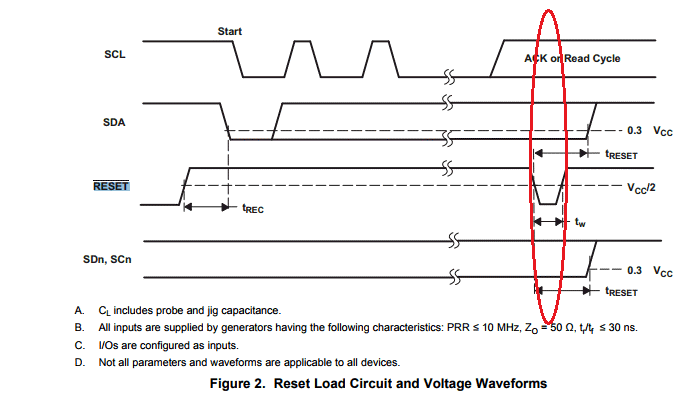

In datasheet page 10, there is a figure like below. When this chip is under reset, what status would the MOS signed with red be? OPEN? CLOSE? UNCERTAIN?