Part Number: UCC21520

Other Parts Discussed in Thread: TIDA-01159

Hi, everyone,

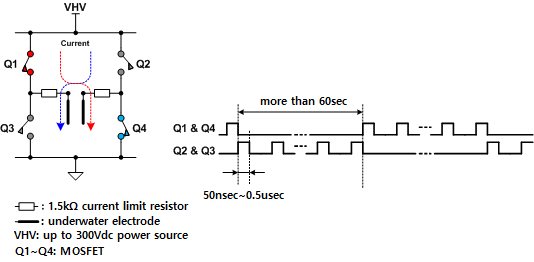

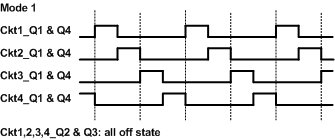

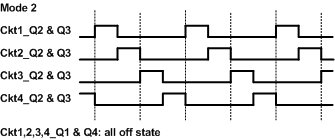

I would like to use the UCC21520 isolated gate driver to operate as shown below.

However, I can not control the high-side mos-fet because bootstrap does not work.

Please let me know how I can control this high-side mos-fet with UCC21520 (or a replacement).

Circuit attached with pdf file.

Thank you.