Hi every one,

My circuit is the same half bridge as the circuit in the datasheet as shown below, and the device values are as follows.

Rin=51Ω, Rdt=4.7KΩ, Rboot=Ron=1Ω, Roff=0Ω, Rgs=10KΩ

Cin=33pF, Cvcc=(1.0+0.1)μF, Cdt=2.2nF, Cboot=(1.0+0.22)μF,

Cvdd=(10+0.22+0.1)μF, Chv=(4.7+0.1) μF/450V

MOS-FET=STD1NK60T4(600V, 1.0A, 8.5Ω),

Dboost=MURA160T3G(600V, 1.0A), Doff=Mss1P4(40V, 1.0A)

And Vcc=3.3V, Vdd=12V, Vhv=20~300V

I have two questions.

The first is dead time related questions.

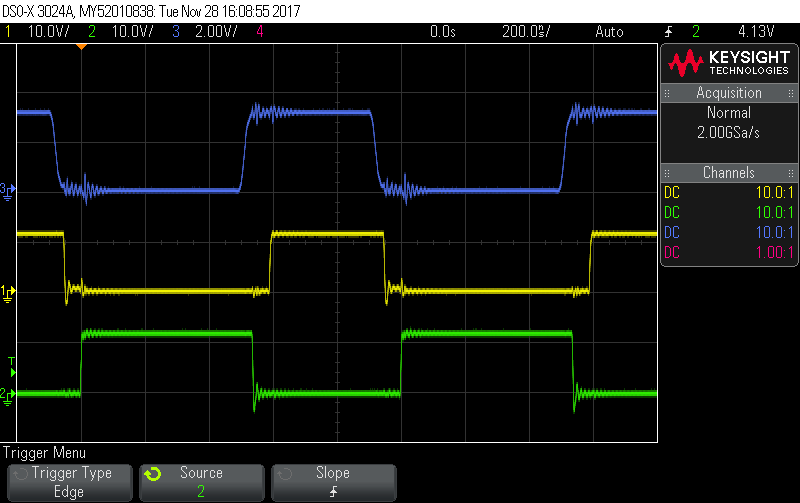

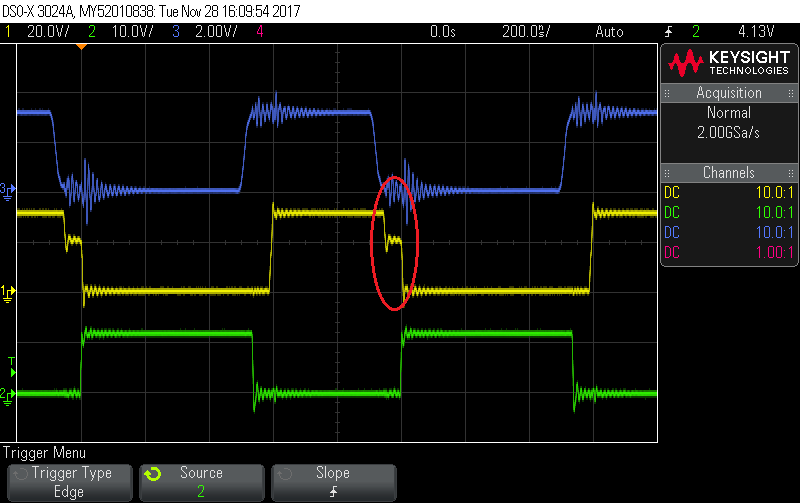

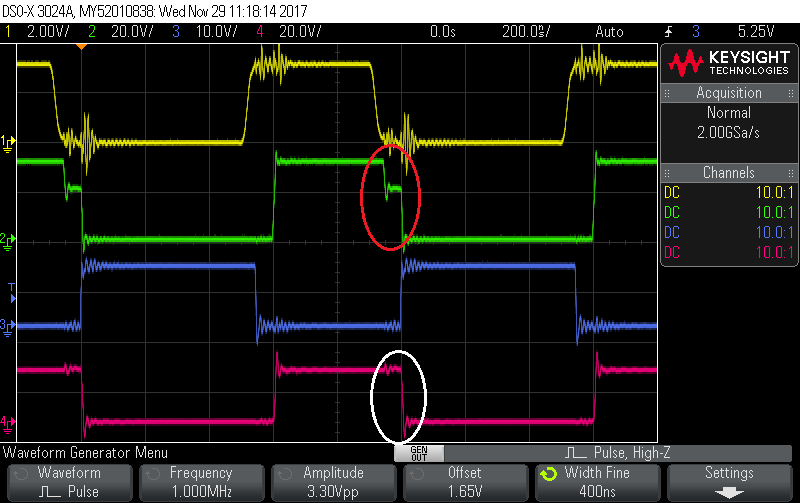

As shown in Figure 1) and Figure 2) below, there is a difference in the dead time waveform between when the high voltage is not applied and when the voltage is applied.(marked red circle).

In what situations does this happen?

Figure 1) Waveform without high voltage

Figure 2) Waveform with 20V high voltage

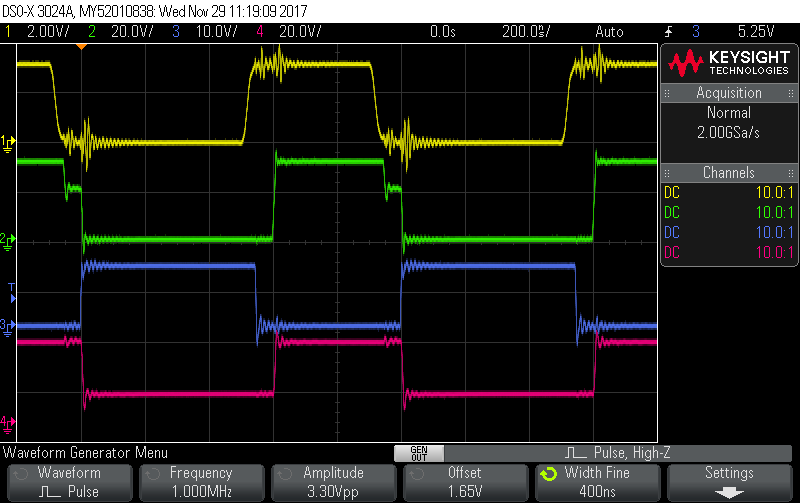

The second question is about the heat of the MOS-FET.

If a high voltage of 100V is applied, the MOS-FET will generate excessive heat under no-load conditions (ie, when the SW output terminal is open). At this time, the high voltage current is about 13mA.

I want to know the cause of the current flowing and the heat generated the MOS-FET in the no-load state.

Best regards,

Kwon