Part Number: DS90CR217

Other Parts Discussed in Thread: DS90CR218A

Dear Team,

My customer is facing an issue with the DS90CR217 regarding data transmission.

You can see below the detail of the issue, sent by my customer :

============================================================================

I use serial interface Channel Link with the components DS90CR217 and DS90CR218.

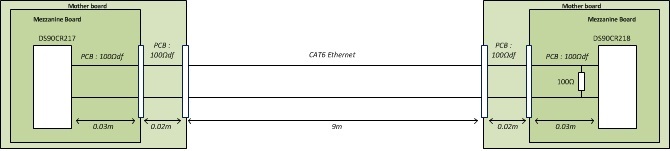

The receiver DS90CR218 is connected to the transmitter DS90CR217 through 9m of Ethernet S/FTP CAT6 cable (differential impedance: 100 ohms).

The differential traces on PCB and the termination resistors are 100 ohms.

This configuration doesn't work.

Indeed, the received data have many errors compared to the generated data.

I have to extend the clock pair of 10cm compared to the 3 pairs of data, in order the have a correct reception.

Do you have any advice on this problem?

What is the maximum length that you have tested with those components? And what kind of cable did you use?

============================================================================

Could you please help us with that.

Thanks in advance for your help.

Best regards,

Bilal MALIK