Other Parts Discussed in Thread: DS280DF810, DS280DF810EVM

rt Number: DS280DF810

HI Sir

1. When I use PRBS15 pattern input DS280DF810EVM ,the CDR can't locked

Do you have idea about this issue ( PRBS15 Pattern as attached file)

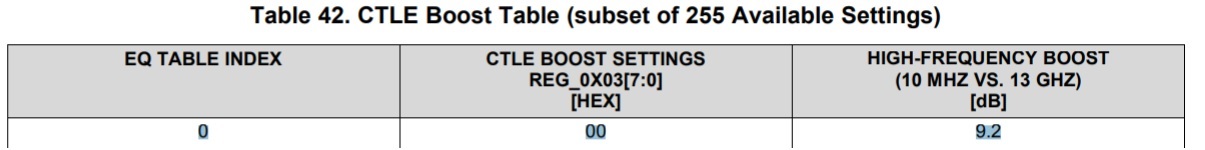

2. Have any register can disable CTLE and VGA function? I would like to bypass CTLE and VGA function without any EQ or something else

3. May I know below register address ?